Advances in

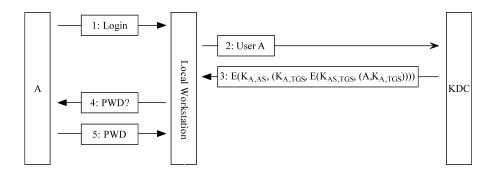

# COMPUTERS

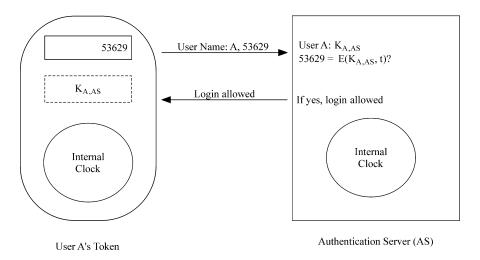

Volume 61

Architectural Issues

Edited by

MARVIN V. ZELKOWITZ

# Advances

# in COMPUTERS VOLUME 61

This Page Intentionally Left Blank

# Advances in **COMPUTERS**

# **Architectural Issues**

EDITED BY

MARVIN V. ZELKOWITZ

Department of Computer Science and Institute for Advanced Computer Studies University of Maryland College Park, Maryland

VOLUME 61

Amsterdam Boston Heidelberg London New York Oxford Paris San Diego San Francisco Singapore Sydney Tokyo ELSEVIER B.V. Sara Burgerhartstraat 25 P.O. Box 211, 1000 AE Amsterdam The Netherlands

ELSEVIER Ltd The Boulevard, Langford Lane Kidlington, Oxford OX5 1GB, UK ELSEVIER Inc. 525 B Street, Suite 1900 San Diego, CA 92101-4495 USA

ELSEVIER Ltd 84 Theobalds Road London WC1X 8RR, UK

© 2004 Elsevier Inc. All rights reserved.

This work is protected under copyright by Elsevier Inc., and the following terms and conditions apply to its use:

### Photocopying

Single photocopies of single chapters may be made for personal use as allowed by national copyright laws. Permission of the Publisher and payment of a fee is required for all other photocopying, including multiple or systematic copying, copying for advertising or promotional purposes, resale, and all forms of document delivery. Special rates are available for educational institutions that wish to make photocopies for non-profit educational classroom use.

Permissions may be sought directly from Elsevier's Rights Department in Oxford, UK: phone (+44) 1865 843830, fax (+44) 1865 853333, e-mail: permissions@elsevier.com. Requests may also be completed on-line via the Elsevier homepage (http://www.elsevier.com/locate/permissions).

In the USA, users may clear permissions and make payments through the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, USA; phone: (+1) (978) 7508400, fax: (+1) (978) 7504744, and in the UK through the Copyright Licensing Agency Rapid Clearance Service (CLARCS), 90 Tottenham Court Road, London W1P 0LP, UK; phone: (+44) 20 7631 5555, fax: (+44) 20 7631 5550. Other countries may have a local reprographic rights agency for payments.

### Derivative Works

Tables of contents may be reproduced for internal circulation, but permission of the Publisher is required for external resale or distribution of such material. Permission of the Publisher is required for all other derivative works, including compilations and translations.

### Electronic Storage or Usage

Permission of the Publisher is required to store or use electronically any material contained in this work, including any chapter or part of a chapter.

Except as outlined above, no part of this work may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without prior written permission of the Publisher.

Address permissions requests to: Elsevier's Rights Department, at the fax and e-mail addresses noted above.

### Notice

No responsibility is assumed by the Publisher for any injury and/or damage to persons or property as a matter of products liability, negligence or otherwise, or from any use or operation of any methods, products, instructions or ideas contained in the material herein. Because of rapid advances in the medical sciences, in particular, independent verification of diagnoses and drug dosages should be made.

First edition 2004

Library of Congress Cataloging in Publication Data A catalog record is available from the Library of Congress.

British Library Cataloguing in Publication Data A catalogue record is available from the British Library.

ISBN: 0-12-012161-1 ISSN (Series): 0065-2458

⊗ The paper used in this publication meets the requirements of ANSI/NISO Z39.48-1992 (Permanence of Paper).

Printed in Great Britain.

# **Contents**

| -                                | NTRIBUTORS                                                                                                                                                                                                                                                                                            | 1X<br>Xiii                               |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

|                                  | Evaluating Software Architectures                                                                                                                                                                                                                                                                     |                                          |

|                                  | Roseanne Tesoriero Tvedt, Patricia Costa, and Mikael Lindvall                                                                                                                                                                                                                                         |                                          |

| 2. 3. 4. 5. 6.                   | Introduction Software Architecture Software Architectural Evaluation A Process for Implementation-Oriented Software Architectural Evaluation Case Studies Summary and Future of Architectural Evaluation Acknowledgements References  fficient Architectural Design of High Performance Microprocesso | 2<br>3<br>6<br>9<br>14<br>40<br>41<br>41 |

|                                  | Lieven Eeckhout and Koen De Bosschere                                                                                                                                                                                                                                                                 |                                          |

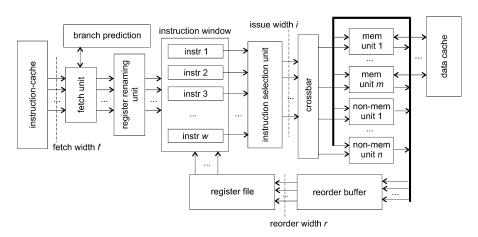

| 2.<br>3.<br>4.<br>5.<br>6.<br>7. | Introduction Out-of-Order Architecture Current Practice Architectural Simulation Reducing the Total Simulation Time Reducing the Design Space Reducing the Workload                                                                                                                                   | 46<br>48<br>50<br>51<br>54<br>55<br>66   |

| 9.                               | Reducing the Length of a Program Simulation Run                                                                                                                                                                                                                                                       | 75<br>99<br>100<br>101                   |

vi CONTENTS

| Security Issues and Solutions in Distributed Heterogeneous | Mobile |

|------------------------------------------------------------|--------|

| Database Systems                                           |        |

| ΔF | R. Hurson | J. | Ploskonka, | Y Jiao | and H | Haridas |

|----|-----------|----|------------|--------|-------|---------|

|    |           |    |            |        |       |         |

|                            | A.R. Hurson, J. Ploskonka, Y. Jiao, and H. Haridas                                                                                                                                 |                                                      |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 2.<br>3.<br>4.             | Introduction and Motivation Security Issues of Centralized Database Systems Security Issues of Multidatabase Systems Mobile Data Management Conclusions Acknowledgement References | 108<br>110<br>139<br>170<br>189<br>191<br>191        |

|                            | Disruptive Technologies and Their Affect on Global Telecommunications                                                                                                              |                                                      |

|                            | Stan McClellan, Stephen Low, and Wai-Tian Tan                                                                                                                                      |                                                      |

| 2.<br>3.<br>4.<br>5.<br>6. | Background & Motivation Quality of Service: Packet vs. Circuit Commodity Bandwidth Commodity Software Commodity Computing Elements Protocols of Significance Conclusion References | 200<br>201<br>215<br>232<br>246<br>259<br>270<br>271 |

|                            | Ions, Atoms, and Bits: An Architectural Approach to Quantum Computing                                                                                                              |                                                      |

|                            | Dean Copsey, Mark Oskin, and Frederic T. Chong                                                                                                                                     |                                                      |

| 2.<br>3.<br>4.<br>5.<br>6. | Introduction                                                                                                                                                                       | 276<br>278<br>287<br>290<br>293<br>305<br>308        |

| CONTENTS | , | /ii |

|----------|---|-----|

|          |   |     |

| 8. System Bandwidth |     |   |    |   |    |   |   |    |    |    |    |  |  |  |  |  |  |  |  |  | 313 |

|---------------------|-----|---|----|---|----|---|---|----|----|----|----|--|--|--|--|--|--|--|--|--|-----|

| 9. Conclusion       |     |   |    |   |    |   |   |    |    |    |    |  |  |  |  |  |  |  |  |  | 314 |

| Acknowledgements    | S . |   |    |   |    |   |   |    |    |    |    |  |  |  |  |  |  |  |  |  | 315 |

| References          |     |   |    |   |    |   |   |    |    |    |    |  |  |  |  |  |  |  |  |  | 315 |

| A                   |     |   |    |   |    |   |   |    |    |    |    |  |  |  |  |  |  |  |  |  | 210 |

| AUTHOR INDEX        |     |   |    |   |    |   |   |    |    |    |    |  |  |  |  |  |  |  |  |  | 319 |

| SUBJECT INDEX       |     |   |    |   |    |   |   |    |    |    |    |  |  |  |  |  |  |  |  |  | 327 |

| CONTENTS OF VOLUM   | ES  | П | N. | T | НΙ | S | S | ΕI | RΙ | ES | 5. |  |  |  |  |  |  |  |  |  | 343 |

This Page Intentionally Left Blank

# **Contributors**

**Koen De Bosschere** is a Professor at the Faculty of Applied Sciences of Ghent University, where he teaches courses in computer architecture, operating systems and declarative programming languages. His research interests include logic programming, system programming, parallelism and debugging. De Bosschere received his PhD in Applied Sciences from Ghent University in 1992. Contact him at kdb@elis.UGent.be.

**Frederic T. Chong** is an Associate Professor of Computer Science and a Chancellor's Fellow at the University of California at Davis. He received his BS in 1990, MS in 1992, and PhD in 1996 in Electrical Engineering and Computer Science from MIT and is a recipient of the National Science Foundation's CAREER award. His current work focuses on architectures and applications for novel computing technologies.

**Dean Copsey** is a doctoral student in Computer Science at the University of California at Davis. He received his BS in 1986 in Chemical Engineering and his MS in 1996 in Computer Science, both from the University of California at Davis. His current research interests include quantum-computing architectures, fault tolerance in nanoscale transistor technologies, and tile architectures for digital signal processing.

Patricia Costa is a scientist at the Fraunhofer Center for Experimental Software Engineering, Maryland. She has a B.Sc. in 1996 and a M.Sc. in 1999 in Computer Science from the Federal University of Minas Gerais, Brazil and a M.Sc. in Telecommunications Management in 2001 from University of Maryland University College. Her research interests include software architecture, agile methods and knowledge management. Contact her at pcosta@fc-md.umd.edu.

**Lieven Eeckhout** is a Postdoctoral Fellow of the Fund for Scientific Research—Flanders (Belgium) (F.W.O. Vlaanderen) in the Department of Electronics and Information Systems at Ghent University, Belgium. His research interests include computer architecture, performance analysis and workload characterization. He obtained his PhD in Computer Science and Engineering from Ghent University in December 2002. Contact him at leeckhou@elis.UGent.be.

**H. Haridas** received his Masters degree in Computer Science and Engineering from the Pennsylvania State University in May 2003 and joined the Automation and Con-

trol IS department at Honeywell as an engineer. His thesis at Penn State covers issues in Wireless medium, Security, and Multi-databases. Harshal received his bachelor's degree in Computer Engineering from Pune Institute of Computer Technology.

**A.R. Hurson** is a Computer Science and Engineering professor at The Pennsylvania State University. NSF, NCR CORP., DARPA, IBM, Lockheed Martin, ONR, and Penn State University have supported his research for the past 20 years. He has published over 200 technical papers in areas including database systems, multidatabases, object oriented databases, security, mobile computing environment, computer architecture and cache memory, parallel and distributed processing, dataflow architectures, and VLSI algorithms.

**Y. Jiao** is a Ph.D. candidate at the Computer Science Department, Pennsylvania State University. She received the B.Sc. degree from Civil Aviation Institute of China, Tianjin, China and the M.Sc. degree from the Pennsylvania State University, State College, Pennsylvania, in 1997 and 2002, respectively, both in computer science. Her main research interests are mobile data access system security, mobile agent security, and energy-efficient information system design.

Mikael Lindvall is a scientist at Fraunhofer Center for Experimental Software Engineering, Maryland. He specializes in work on software architecture and impact analysis as well as experience and knowledge management in software engineering. He is currently working on defining cost-efficient approaches to evaluate software architectures. He received his PhD in Computer Science from Linköpings University, Sweden. His PhD work was based on a commercial development project at Ericsson Radio and focused on the evolution of object-oriented systems. Contact him at mlindvall@fc-md.umd.edu.

**Stephen Low** is a Distinguished Technologist in the Carrier Grade Systems group at Hewlett Packard. During his 12 years at HP, Compaq and Tandem, he has been a principal architect of several high availability platforms used in core telecommunications applications. He holds several patents in this area and has multiple publications. Prior to joining HP, he was a member of technical staff at AT&T Bell Labs, GPT and Northern Telecom. Dr. Low holds a Ph.D. in theoretical physics from the University of Texas at Austin.

**Stan McClellan** is a Distinguished Technologist in the Carrier-Grade Systems group at Hewlett Packard. In this capacity, he is responsible for the architectural definition of next-generation communication systems. Prior to joining HP, he held various positions in aerospace, academia, and telecommunications industries. Dr. McClellan holds a Ph.D. in Electrical Engineering from Texas A&M University.

**Mark Oskin** is an Assistant Professor at the University of Washington in Computer Science and Engineering. His current research interests include quantum architec-

tures and languages, and scalable execution substrates for future silicon technologies.

**J. Ploskonka** is a master's student at the Pennsylvania State University studying computer science and engineering. She received a bachelor's degree in electrical engineering from Grove City College. Her research interests include security and sensor networks.

**Wai-tian Tan** is a member of the Media Communications and Networking Department in HP Labs. He received the BS degree from Brown University in 1992, the MSEE degree from Stanford University in 1993 and the Ph.D. degree from U.C. Berkeley in 2000. He worked for Oracle Corporation from 1993 to 1995. His research focuses on adaptive media streaming, both at the end-point and inside the delivery infrastructure.

Roseanne Tesoriero Tvedt is a scientist at the Fraunhofer Center for Experimental Software Engineering, Maryland and President and founder of the software development company Pan Orange, Inc. She received Masters and Ph.D. degrees in Computer Science from the University of Maryland. Her research interests include software architecture evaluation, agile methods, knowledge management, and computer science education. She can be reached at rtvedt@fc-md.umd.edu or rtvedt@panorange.com.

This Page Intentionally Left Blank

# **Preface**

In this volume of the **Advances in Computers** we present five chapters on computer architecture. The chapters discuss both how to develop new computing platforms that take advantage of new technology and how to evaluate the software that is being designed on those platforms. This series of books, the present one being volume 61, dates from 1960 and is the longest continuously published collection that chronicles the advances and ever changing computer landscape.

In Chapter 1, "Evaluating software architectures," Roseanne Tesoriero Tvedt, Patricia Costa, and Mikael Lindvall present a method for evaluating the designs of a software system. They present a seven-step process for evaluating a design looking for discrepancies between the abstracted design they develop and the system that has been implemented. Their process then suggests changes to the source code that will put the system in compliance with the design they develop. Having both synchronized should greatly aid in maintaining that system in the future. They present two case studies of using their process on existing products.

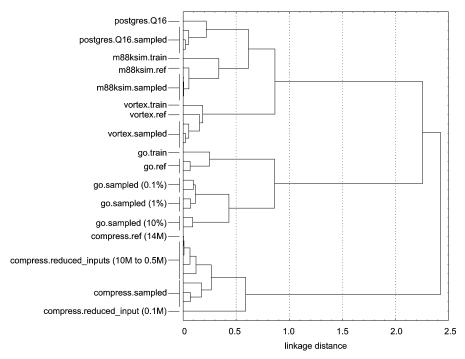

Lieven Eeckhout and Koen De Bosschere present "Efficient architectural design of high performance microprocessors" in Chapter 2. They present a new simulation methodology for designing high performance microprocessors by combining several recently proposed techniques, such as statistical simulation, representative workload design, trace sampling and reduced input sets. They show how simulation of these new designs can be made efficient by selecting a limited but representative workload, by applying trace sampling and reduced input sets to limit the simulation time per benchmark, and by optimizing the architectural simulators.

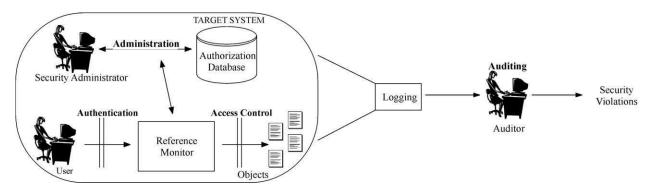

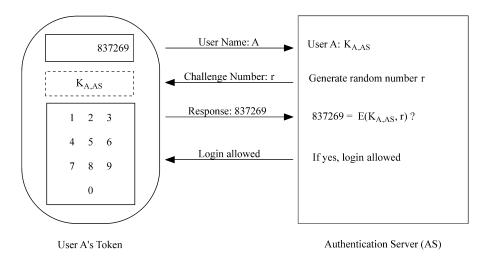

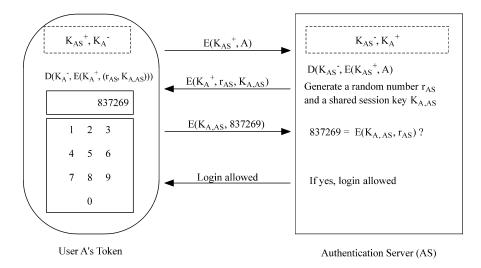

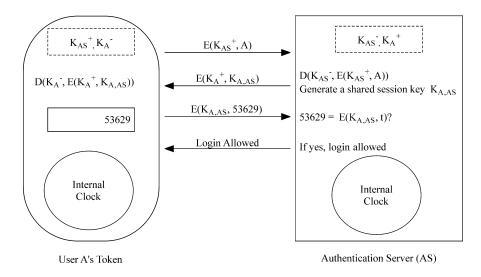

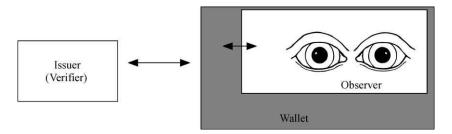

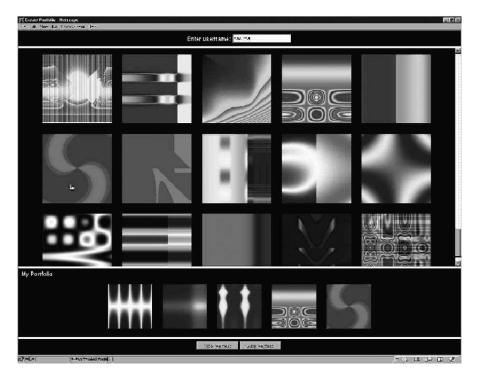

Chapter 3 contains "Security issues and solutions in distributed heterogeneous mobile data systems" by A. R. Hurson, J. Ploskonka, Y. Jiao and H. Haridas. With increased use of mobile computing resources and centralized databases, security of these systems is of growing importance. When wireless communication links and mobility are introduced, adapting existing methods may not be satisfactory, especially where mobile devices are already resource-poor. New techniques are needed to handle the constraints introduced by mobile systems.

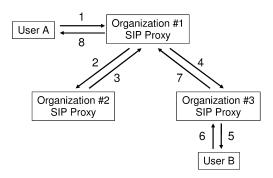

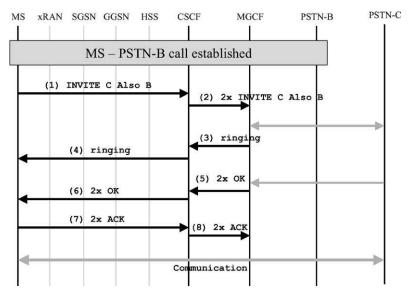

In Chapter 4 "Disruptive technologies and their affect on global telecommunications" by Stan McClellan, Stephen Low, and Wai-Tian Tan, the authors categorize

xiv PREFACE

several key technologies, platforms, and services which are affecting the evolution of telecommunications networks. With much standardization of these hardware, operating systems, and telecommunications services across the industry, they survey issues related to quality of service in packet-switched networks and some key protocols affecting the structure and operation of telephony networks.

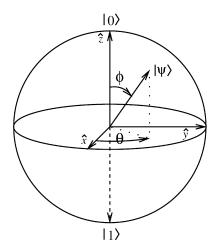

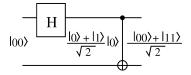

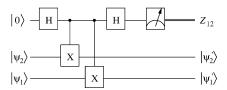

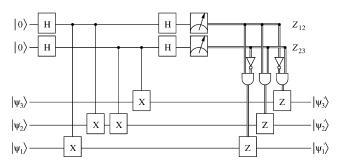

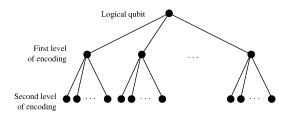

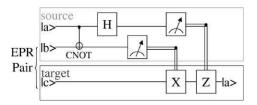

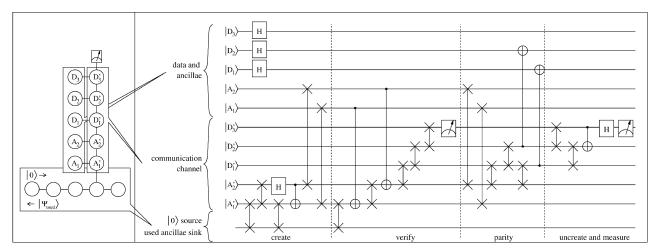

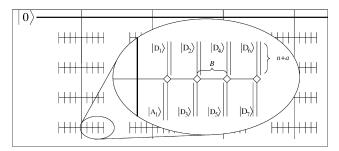

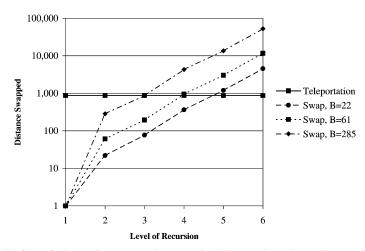

As microprocessors have become faster and smaller, the ultimate size and speed reduction has been the dream of using atoms and molecules to store information. This is the realm of quantum computing. In the last chapter of this volume "Ions, atoms, and bits: An architectural approach to quantum computing," the authors Dean Copsey, Mark Oskin, and Frederick T. Chong discuss architectural issues in quantum computing. Unlike classical signals, quantum data cannot be transmitted over a wire, but must be move step-wise from location to adjacent location. They compare the swapping channel with a longer-range teleportation channel and discuss error correction, which is necessary to avoid data corruption.

I hope that you find this volume of use in your work or studies. If you have any suggestions of topics for future chapters, or if you wish to contribute such a chapter, I can be reached at myz@cs.umd.edu

Marvin Zelkowitz University of Maryland, College Park, MD, USA

# **Evaluating Software Architectures**

# ROSEANNE TESORIERO TVEDT, PATRICIA COSTA, AND MIKAEL LINDVALL

Fraunhofer Center for Experimental Software Engineering College Park, MD 20740 USA rtvedt@fc-md.umd.edu pcosta@fc-md.umd.edu mlindvall@fc-md.umd.edu

### Abstract

As software systems become increasingly complex, the need to investigate and evaluate them at high levels of abstraction becomes more important. When systems are very complex, evaluating the system from an architectural level is necessary in order to understand the structure and interrelationships among the components of the system. There are several existing approaches available for software architecture evaluation. Some of these techniques, pre-implementation software architectural evaluations, are performed before the system is implemented. Others, implementation-oriented software architectural evaluations, are performed after a version of the system has been implemented. This chapter briefly describes the concepts of software architecture and software architectural evaluations, describes a new process for software architectural evaluation, provides results from two case studies where this process was applied, and presents areas for future work.

| 1. | Introduction                                                            | 2          |

|----|-------------------------------------------------------------------------|------------|

| 2. | Software Architecture                                                   | 3          |

|    | 2.1. Sample Definitions                                                 | 3          |

|    | 2.2. Definitions Used in this Chapter                                   |            |

| 3. | Software Architectural Evaluation                                       | $\epsilon$ |

|    | 3.1. Pre-Implementation Software Architectural Evaluations              | $\epsilon$ |

|    | 3.2. Implementation-Oriented Software Architectural Evaluations         | 7          |

| 4. | A Process for Implementation-Oriented Software Architectural Evaluation | 9          |

|    | 4.1. Background                                                         | ç          |

|    | 4.2. Definition of the Process Steps                                    | (          |

|    | 4.3. Use of the Process                                            | 13 |

|----|--------------------------------------------------------------------|----|

| 5. | Case Studies                                                       | 14 |

|    | 5.1. Perspective for Evaluation—Maintainability                    | 15 |

|    | 5.2. Definition of Metrics                                         | 15 |

|    | 5.3. Representing the Architecture                                 | 18 |

|    | 5.4. Case Study 1—the VQI                                          | 20 |

|    | 5.5. Case Study 2—Proprietary Design, Simulation and Analysis Tool | 28 |

| 6. | Summary and Future of Architectural Evaluation                     | 40 |

|    | Acknowledgements                                                   | 41 |

|    | References                                                         | 41 |

### 1. Introduction

In the early days of software development, much attention was given to issues related to the design of algorithms and data structures. This emphasis on algorithms and data structures was due in part to the fact that programming language features were closely related to the hardware and it was difficult to abstract and reason about systems at a higher level. As more sophisticated features were added to programming languages, it became easier to create more complex systems. As systems became increasingly complex, the ability to reason about systems at higher levels of abstraction became progressively more important. The shift in design concerns is evident in an early paper by Deremer and Kron [16] where the authors describe the difference between programming-in-the-small and programming-in-the-large and argued for a Module Interconnection Language (MIL) to help describe a system at an architectural level. Since that time, programming languages have become even more sophisticated and the use of networked components has become more prevalent. With ever increasing system complexity, the need to examine and evaluate systems at higher levels of abstraction becomes essential.

Software architectural evaluation techniques provide mechanisms for reasoning about systems at the architectural level. These techniques examine the structure and behavior of a system utilizing a high-level view. They are used to identify strengths and inadequacies in architectural designs.

In Section 2 of this chapter, the main concepts of software architecture are introduced. Section 3 discusses various types of software architectural evaluation techniques. Section 4 presents the details of a new process for software architectural evaluation. Section 5 describes several case studies where this process was used. Finally, Section 6 presents a summary and describes several opportunities for future work.

## 2. Software Architecture

Many definitions of software architecture exist; however, there is no universally accepted definition. The lack of a standard definition often leads to confusion making a discussion of the definition of software architecture necessary before the topic of architectural evaluation can be introduced.

# 2.1 Sample Definitions

Although there are many definitions of software architecture, common themes and ideas run through these definitions. Many of the definitions include the concept of components or modules and the communication mechanisms among components. For example, Perry and Wolf [28] define software architecture by describing three classes of architectural elements: processing elements, data elements and connection elements. Data elements contain the information that is processed, used and manipulated by the processing elements. The connection elements are the parts of the system that connect the pieces of the system together. Bass, Clements, and Kazman [6] describe software architecture as the structure or structures of the system comprised components and externally visible properties and relationships among them. This definition implies that the internals of each component do not play a role in software architecture. Crispen and Stuckey [15] define software architecture as a partitioning strategy and a coordination strategy. The partitioning strategy defines how the system is divided (or composed) of components. The coordination strategy defines how the components of the system interface with each other. This definition for software architecture incorporates the ideas of constraints and rationale for how components are put together and how the communication should occur. Including the ideas of constraints and rationale is common in many definitions of software architecture. The Bass, Clements, and Kazman definition implies that behavior is part of the architecture. Clements and Kogut [14] include constraints and rationale in their definition of software architecture. Booch, Rumbaugh and Jacobson [10] also include constraints in their definition of software architecture. In several definitions, the concept of parameterized components that can be altered to form new applications is included. Bhansali [9] calls this type of architecture generic software architecture. The idea of a generic architecture seems to lead toward the concepts of architectural styles and design patterns as described in [20] and [19] respectively. Architectural styles and design patterns are important concepts in the architectural evaluation process that will be described later.

<sup>&</sup>lt;sup>1</sup>The Software Engineering Institute maintains a list of definitions for software architecture and a related bibliography at http://www.sei.cmu.edu/architecture/definitions.html.

In some cases, software architecture is viewed from different levels or various perspectives. For example, Soni, Nord, and Hofmeister [31] describe four perspectives of software architecture: the conceptual architecture, the module interconnection architecture, the execution architecture, and the code architecture. The conceptual architecture describes the major design elements of the system and the relationships among them. The module interconnection architecture encompasses the functional decomposition of the system and its layers. The execution architecture describes the dynamic structure of the system. The code architecture describes how the source code of the system is organized. Kruchten [23] describes a 4+1 (logical, process, physical, development, and use-case scenarios) view of software architecture. The views of the Kruchten model of software architecture are similar to those of Soni, Nord and Hofmeister. However, Kruchten includes use-case scenarios as an additional view of the software architecture.

# 2.2 Definitions Used in this Chapter

The definitions used in this chapter are based on common elements from the definitions of software architecture described in the previous section. Software architecture deals with the structure and interactions of a software system. The most basic building blocks of the structure of software architecture are components and the interrelationships among the components. In addition to structure, behavior is part of software architecture. Constraints and rules describe how the architectural components communicate with one another. The software architecture of a system may be viewed at different levels for different purposes.

Even at the conceptual or logical level, architectural components can be viewed at several different abstraction levels and vary based on the size of the system. At the highest level, the components are the subsystems, which in the case of a very large system, can be a complex system and can have subsystems of their own. Subsystems are often formed by lower level components, which are, in the case of an object-oriented system, collections of classes. In order for the architectural components to form a system, they must communicate with each other, creating interrelationships or connectors. The division of a system into smaller building blocks is based on the philosophy of "divide and conquer" which lets the implementer divide the problem into smaller and less complex pieces.

When viewed at the highest levels, a system's architecture is referred to as the macro-architecture of the software system. At lower levels of abstraction, it is referred to as micro-architecture. Architectural styles and design patterns are similar to what Bhansali [9] describes as generic forms of software architecture. Often architectural styles guide the structure and interactions of the system when describing

the software architecture of a system at the macro-architectural level. When describing the structure and/or interactions of a system at a micro-architectural level, often design patterns can be used.

# 2.2.1 Macro-Architecture—Architectural Styles

In Garlan and Shaw [20], several basic architectural styles are defined. One example is a client-server architectural style in which the application is divided into two major subsystems that communicate with each other. Other examples of architectural styles include layered and piped architectures. Each architectural style brings not only certain properties to the system, but also implicit and explicit implications and tradeoffs that translate into design rules and guidelines. The client-server architectural style, for example, divides the system into a "front-end client" and a "back-end server" allowing for a separation of concerns on a high level. This style results in a design guideline that restricts the communication between the client and the server to a common and narrow interface. The layered architecture has similar properties. It allows encapsulation of low-level functions and the establishment of an abstract machine that builds on the services lower layers offer. An implication of a layered architecture is, for example, that high level layers can only use services of lower level layers and not vice versa. Restricting communications to the layers directly below is another example of a rule that might follow from this choice in architectural style.

# 2.2.2 Micro-Architecture—Design Patterns

Design patterns methodically name, explain, and evaluate important and frequent designs in object-oriented systems. Design patterns "solve specific design problems and make object-oriented designs more flexible and elegant, and ultimately reusable. They help designers reuse successful designs by basing new designs on prior experience. A designer who is familiar with such patterns can apply them immediately to design problems without having to rediscover them" [19]. One example of a design pattern is the mediator that encapsulates how a set of objects interacts. Another example is the observer that typically is used to provide various views of the same subject data. The mediator and the observer are described and exemplified respectively in Sections 5.4 and 5.5. Design patterns are sometimes referred to as microarchitectural styles and contribute to an organized system structure. In each system, several design patterns can be used, and they can coexist with each other and with different architectural styles. By selecting a design pattern, certain architectural implications and tradeoffs follow. Some of these tradeoffs and implications are described at a high level in [19]; however, context-specific implications and tradeoffs may exist and result in implicit and explicit design rules and guidelines.

Typically, design patterns are discussed at the class level putting them into the category of micro-architecture. However, the concepts in some design patterns can be abstracted to the component level. To incorporate the ideas of design patterns into this higher-level view of software architecture, the class roles of a design pattern are abstracted to the component level. For example, in the Observer pattern, the role of the Subject class can be played by a component of classes representing the subject data to be observed by Observer components. Similarly, with the Mediator pattern, a set of classes (i.e., a component) may represent a Colleague in the pattern.

# 3. Software Architectural Evaluation

Software architectural evaluations are investigations into how a system is structured and behaves with the purpose of suggesting areas for improvement or understanding various aspects of a system (e.g., maintainability, reliability, or security). In many cases, a software architectural evaluation is performed before a system has been designed or implemented. Often, this type of architectural evaluation is performed to compare alternatives or to determine whether or not the architecture is complete or appropriate for the application. In other cases, a software architectural evaluation is performed after the system has been implemented. This type of architectural evaluation typically is performed to make certain that the actual implementation of a system matches the planned architectural design.

# 3.1 Pre-Implementation Software Architectural Evaluations

A software architectural evaluation that occurs prior to the implementation of a software system is referred to here as pre-implementation software architectural evaluation. Pre-implementation software architectural evaluation is used to evaluate one or more software architectural candidates or to evaluate various properties of an architecture. Pre-implementation software architectural evaluations, as described by Abowd et al. [1] and Avritzer and Weyuker [3], can be based on the description of the software and other sources of information such as interviews with the designers of the software architecture. With these methodologies, scenarios are often used to determine the adequacy of the software architecture. A scenario is a series of steps that describes the use or a modification to the system from the point of view of different stakeholders. Scenarios are used to highlight potential weaknesses and strengths of the architecture and are useful for concretizing requirements of the system and understanding non-functional requirements. An example of a scenario is: when a data exception occurs, all users should be notified by e-mail immediately. This scenario indicates that the system should be reliable. Scenarios like these should be

taken into account when evaluating the architectures so that the best solutions are chosen. The methodology proposed by Yacoub and Ammar [34] analyses architectures from a risk perspective early in the life cycle to assess whether the system will have the desired qualities or quality attributes (e.g., performance, reliability, and maintainability). Bengtsson and Bosch's architectural level prediction of software maintenance is another example of the same kind of analysis [8]. The approach suggested by de Bruijn and van Vliet [11] is based on generating a basic architecture that is immediately evaluated to identify problems. The cycle of generating and evaluating the software architecture is repeated. This iterative approach continues until the architecture fulfills the software requirements. The Architecture-Level Modifiability Analysis (ALMA) model by Lassing et al. [24] emphasizes that a goal should govern how the evaluation of the software architecture is carried out. ALMA makes a distinction between three different goals for evaluation: risk assessment, maintenance cost prediction, and software architecture comparison. Architectural evaluations with the goal of risk assessment focus on finding types of changes for which the system is inflexible. For maintenance cost prediction, software architectural evaluations estimate the cost of maintenance effort for the system during a given period. When software architecture comparison is the goal of the evaluation, two or more candidate software architectures are compared to find the most appropriate one. Additional software architectural evaluation approaches are described in Dobrica and Niemela [17].

# 3.2 Implementation-Oriented Software Architectural Evaluations

Implementation-oriented software architectural evaluation is a term used to describe the evaluation of software architecture after a version of the system has been implemented. Since this type of software architectural evaluation is performed after a version of the system exists, it can utilize data measured from the actual source code and associated documentation. Implementation-oriented software architectural evaluations can be used for similar goals to pre-implementation software architectural evaluations. For example, the source code and associated documentation can be used to reconstruct the actual software architecture in order to compare it to the planned or conceptual software architecture. Recovering the actual architecture of an implemented system can be used for risk assessment and maintenance cost prediction as well. The analysis of the actual software architecture can be used to evaluate whether the implemented software architecture fulfills the planned software architecture and associated goals, rules and guidelines.

A literature survey conducted by Hochstein and Lindvall [21] noted that whereas there are many pre-implementation software architectural evaluation approaches available, there are not many implementation-oriented approaches described in the literature. An early example of an implementation-oriented approach is Schwanke's re-engineering tool [29]. The tool uses a concept of similarity based on Parnas' information hiding principle; but is not designed specifically for object-oriented systems. Murphy et al.'s work with reflexion models [27] is another example of this type of software architectural evaluation. With reflexion models, the designers of the system are interviewed to describe the conceptual view of the implemented system. Next, the actual architecture is recovered to determine if the designer's conceptual view matches the implementation.

Implementation-oriented software architectural evaluation can be combined with pre-implementation software architectural evaluation to achieve different goals. Before implementation occurs, software architectural evaluation is used to assure that certain goals are achieved based on the architectural decisions made. However, in many cases, the implementation of a system differs from the architectural design. That is, the implementation often does not match the planned design. Software systems are subject to changes over their lifetime. When time is spent evaluating architecture to meet certain criteria and to achieve specific quality attributes prior to system implementation, there is a need to assure that each new version of the system indeed matches the planned architecture to harvest the benefits of the initial investment in architectural evaluation. Implementation-oriented software architectural evaluations can be used to make certain that the actual architecture stays on the intended track.

An example of a combination of approaches that would be successful is the combination of the Architecture Trade-off Analysis Method (ATAM) [13] and an implementation-oriented approach like the one described later. The ATAM method uses brainstorming sessions to perform a tradeoff analysis of architectural decisions based on their impact on different quality attributes that are important for different classes of stakeholders. The ATAM method is valuable in an early phase of the development when the design is being created. Once the architecture is evaluated, design decisions are made and these decisions are expected to be implemented in the system. An implementation-oriented approach such as the one described later could be used after a version of the system has been developed to (i) make sure the architecture maintains the properties desired to reach a certain quality attribute and (ii) make sure the implementation conforms to the planned architectural design. Every version of the system can be assessed and evaluated in order to track the architecture and keep it aligned with the design goals.

# 4. A Process for Implementation-Oriented Software Architectural Evaluation

The process defined in this chapter is one that evolved over several iterations of software architecture evaluations. This software architectural evaluation process utilizes the macro-architecture view of a system. The process analyzes the components and their external interfaces with each other. This process is conducted after an implementation of the system exists.

The process defined here is not a substitute for alternate architectural evaluation processes that are typically conducted before a system is implemented. Rather, this process may be used in conjunction with other architectural evaluation techniques to ensure that the system is being implemented in agreement with the recommendations resulting from other forms of architectural evaluation. For example, if an architectural evaluation performed before the system is designed results in a suggestion of a recommended architectural style, the architectural evaluation process described in this section can be used to confirm that the suggested architectural style has been implemented correctly in the actual system.

The process was designed to be relatively quick and used repeatedly to keep the actual implementation of the software architecture consistent with the planned architectural design. It does not assume that documentation of the architectural design exists prior to the evaluation of the system. However, if documentation does not exist prior to the evaluation, the process requires input from the developers of the system to recover the planned architectural design of the system. The architectural evaluation process involves members of the development team and ideally, a separate analysis team. One of the main objectives of this process is to provide useful feedback to the development team without extensively disrupting their daily activities. The members of the development team are used sparingly in this process to confirm the findings of the analysis team.

# 4.1 Background

One of Fraunhofer Center for Experimental Software Engineering, Maryland's (FC-MD) primary assets is a software system, the Visual Query Interface (VQI) [30], which manages experience supporting the Experience Factory approach for organizational learning [4]. In 1999, the system had evolved into a difficult state. Both current and potential users of the system wanted more functionality, but it was clear that the current architecture of the system could not withstand additional changes. Each change to the system became increasingly difficult to make. The effort of adding new functionality widely exceeded expectations and it had become apparent that the

system had decayed [18] to a point its maintenance had become a problem; making it clear that the system need to be restructured.

After the investment in restructuring the system was made, it was important to FC-MD to confirm that the structure of the system had improved and that it had been implemented as planned. The software architectural evaluation process described in the next section was developed to assist with this task.

# 4.2 Definition of the Process Steps

The architectural evaluation process consists of seven process steps. As mentioned previously, one of the main objectives of this process is to provide quick and useful feedback to the developers of a project. To minimize negative schedule effects, it is envisioned that an analysis team, separate from the development team, performs the majority of the work for the evaluation process. The following description of each process step contains information regarding the roles of the development and analysis teams. It is envisioned that this process can be tailored for different contexts using different metrics and representations of the architecture. This subsection provides the basic outline of the steps and describes the roles for the analysis team and the developers. The case studies described in the next section give a more detailed view of how the process could be applied.

# Step 1. Select a Perspective for Evaluation

Architectural evaluations may be conducted with different goals in mind and from many different perspectives. For example, a system might be evaluated to determine whether or not the system implements the specified functional requirements or to determine if it fulfills the non-functional requirements, i.e., the system qualities or quality attributes. Other examples of perspectives are evaluation for security, reliability, performance, and maintainability. Selecting a perspective is important for identifying appropriate goals and measurements for the evaluation process. The GQM technique [5] is used in this step to define goal-oriented metrics based on questions that need to be answered to determine if goals have been achieved. For example, if the perspective chosen is maintainability, goals based on attributes of maintainability such as coupling and cohesion might be identified.

The analysis team performs this step with the help of the development team. The development team provides input on the perspective. The analysis team creates the goals and defines the metrics following the GQM technique. The development team provides feedback to the analysis team on the goals and metrics.

# Step 2. Define Planned Architecture and Guidelines

Once a perspective has been chosen and goals have been identified and elaborated with the GQM technique, the planned architecture of the system is identified and guidelines with associated metrics are defined. These architectural guidelines are used to validate that the architecture possesses desired properties. Often, these guidelines translate into quantitative metrics. For example, if evaluating a system from the perspective of maintainability, guidelines related to coupling might be established. Sample guidelines based on coupling might include the following: coupling between the components should be low; and the extent of the coupling between components should be low. Quantitative metrics measuring coupling between the components and the extent of the coupling are derived from these guidelines. In addition to defining guidelines and metrics based on the perspective of the architectural evaluation, some guidelines and metrics are defined based on the architectural styles and the design patterns chosen for the system.

The analysis team works with one or two representatives of the development team (and/or uses documentation) to identify the planned, high-level architecture of the system. The planned (or ideal/intended) architecture is defined by architectural requirements, by implicit and explicit architectural guidelines and design rules and implications stemming from the use of architectural styles and design patterns. The analysis team needs to recover the different aspects of the planned architecture and create a model of it that will guide the evaluation. Once the high level architecture of the system has been defined, the analysis team uses it to derive the implications, tradeoffs, guidelines, and design rules that result. The analysis team needs to select and customize the guidelines and metrics for the specific context. The selected set of metrics must capture the properties that the team finds most important while, at the same time, being cost-efficient to collect and analyze. As the analysis team learns more about the planned architecture, these guidelines and metrics are commonly iterated and updated during this step.

# Step 3. Recover Actual Architecture

The actual architecture is the high-level structure of the implemented system, its architectural components and their interrelationships, as well as its architectural styles and design patterns. Studying the implementation of the system, which is, to a large extent an abstraction obtained from the source code, represents the actual architecture. It should be noted that this step is not the same as source code analysis, but it is used to identify the static architectural components of the actual system. To perform this step efficiently, the analysis team relies on a set of automated or partially automated tools that help them with this task. In many cases, the tools have to be

defined based on programming language, the measurements that are to be collected, and other factors in the development environment.

Identifying the contents of a component is often one of the key complications involved with the recovery of the high-level architecture of an implemented system. In some cases, programming language features can be used to reduce some of the difficulties associated with this task. With Java, for example, the analysis team can use packages as a way of determining the contents of the system's components. However, not all Java developers use packages and even when packages are used, there is not always a one-to-one correspondence between the packages and the high-level components of the system.

Identifying architectural styles and design patterns is another complication that arises with the recovery of the actual architecture. Architectural styles are not always easy to detect in the actual implementation of a system. Design patterns can be implemented in different ways and can be difficult to detect.

As part of this step of the process, the design team works with one or two members of the development team to partition the files containing the actual implementation of the system into their appropriate components. Then, the analysis team extracts relevant information and computes metrics from the component files to obtain the actual architecture of the system.

# Step 4. Compare Actual to Planned to Identify Architectural Deviations

Architectural deviations are differences between the planned architecture and the actual implemented version of the architecture. These architectural violations are identified by comparing the planned architectural design defined in step two to the abstraction of the actual architecture obtained in step three. Deviations can be missing or extra components, missing or extra connections between components, violations of architectural guidelines, or values of metrics that exceed or do not match a certain expected value.

The analysis team compiles a list of these violations and notes the circumstances under which the violation was detected and the reason the team suspects it is a violation. If necessary, the analysis team conducts a more detailed analysis of the deviation in order to determine its possible cause and degree of severity. The deviations are categorized and patterns of violations are identified.

# Step 5. Verify Violations

Once the analysis team has composed and characterized the list of architectural violations, the list is verified during a discussion with one or two members of the

development team. This step is taken for several reasons. First, it helps to ensure that the analysis team has not incorrectly identified any violations by a misunderstanding of how the system was implemented. Secondly, it gives the development team feedback on how well the actual implementation matches the planned architecture and exposes the general types of deviations that have occurred. Additionally, the analysis team gathers more information on how and why the violations have occurred.

# Step 6. Suggest Changes to Planned and/or Actual Architectures

Based on the results from the previous step, the analysis team formulates high-level change recommendations that would remove the deviations from the system. Sometimes, the deviations result in requests for source code changes. In some cases, the requests are related to changes in the planned architecture or guidelines. It should be noted that it is not the task of the analysis team to design or implement the change requests. Rather, this step is a way for the analysis team to contribute to the improvement of the system in a constructive way by giving feedback to the development team.

# Step 7. Repeat Steps 4–6 After Changes Have Been Implemented

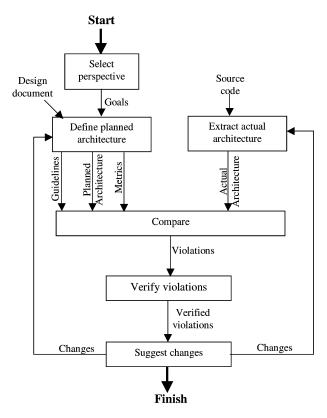

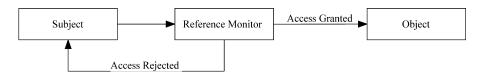

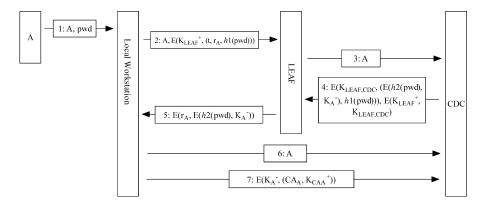

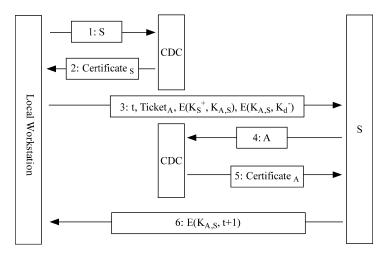

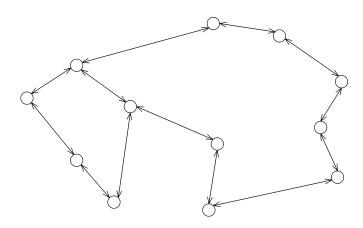

The analysis team discusses the change requests with the development team. It is the role of the development team to decide which changes to implement and how the changes will be implemented. Once the changes have been implemented, it is important to verify that actual architecture complies with the planned one. To verify that the planned and actual architectures are in alignment, the steps of identifying the actual architecture and any architectural deviations are repeated. This verification is done to make sure that the changes have been implemented correctly and that no new violations have been introduced into the system. The steps of the process are shown in Fig. 1.

# 4.3 Use of the Process

The process for software architectural evaluation is designed to be efficient and conducted at various points over the lifetime of a software system. It is expected that one iteration of the evaluation process will be run after a new feature or set of features is implemented. Another important objective in the design of this process was to provide valuable feedback to the development team with minimal disruption to the team's usual activities. The process was designed to fit seamlessly into an existing

FIG. 1. A diagram of the software architectural evaluation process steps.

development environment. The analysis team should perform the bulk of the work needed to conduct the evaluation. Members of the development team should be used to verify the findings of the analysis team in both the definition and recovery of the architecture and implement the recommended changes.

## 5. Case Studies

The software architectural evaluation process was created due to a maintainability problem experienced with a project developed by FC-MD. The architectural evaluation process has been used to analyze several iterations of a FC-MD software tool (VQI) and with one commercial product prior to its release. The commercial prod-

uct is a proprietary system that incorporates the design, simulation and analysis of CAD diagrams. In both of these case studies, the perspective chosen for the evaluation was maintainability, and the metrics and representation of the architecture used in the evaluation were identical. The case studies are presented here in the order in which they were performed. The first case study summarizes the results of several iterations through the evaluation process on the VQI system. The second case study gives a more in-depth description of a single iteration through the evaluation process on the commercial product.

# 5.1 Perspective for Evaluation—Maintainability

With the VQI system, the main goal of the initial re-engineering activity was to create a system that was easier to maintain than the previous version that had degenerated into an inflexible state. The initial architectural evaluation was conducted to recover the actual architecture of the existing decayed system and to verify that the re-engineered system conformed to the new design plans. For each of the following versions, the evaluations were conducted to verify that the changes made to the system did not deviate from the planned architecture and design guidelines.

With the proprietary commercial product, the architectural evaluation was conducted before the product was released for beta testing. The main objective for this evaluation was to verify that the system had been implemented according to the plan and to identify potentially fault-prone components.

In the case study evaluations, coupling was the main characteristic considered for determining maintainability. In both the VQI and the proprietary commercial system, low coupling between components was considered to be desirable. However, based on component characteristics such as the design patterns chosen, several components were expected to have higher coupling than other components of the system. For example, a distinction is made between components that are library-oriented and those that are function-oriented. A library-oriented component is one that is made up of related data structures and routines that are expected to be used by many other components. A function-oriented component is one that implements a specific functional requirement of an application. Given these definitions, high coupling from non-library components to library-oriented components is expected while coupling from library-oriented components to non-library components is undesirable, and the coupling among function-oriented components should be minimized.

# 5.2 Definition of Metrics

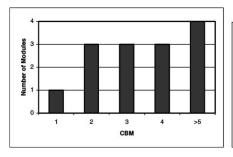

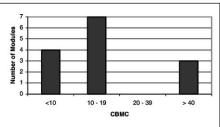

The metrics used in the evaluations were based on the notion of static couplings between modules and classes detected in the source code. Essentially, a general design goal is to reduce the amount of inter-module coupling without increasing the amount of intra-module coupling. To measure the degree of inter-module coupling, two metrics were defined: coupling between modules (CBM) and coupling between module classes (CBMC). A complete description of these metrics and a discussion of how they were derived can be found in [25] and [26].

For the definitions of CBM and CBMC, static coupling is considered. A coupling between two classes occurs when one class uses another class in its implementation. Coupling occurs when the source code of one class includes the definition of another class (e.g., importing in Java and including in C++), includes a declaration of a variable or parameter of another class type, or accesses a data member or method of another class. When the two classes involved in the coupling belong to different components, the coupling represents a coupling between components (or modules).

The CBM metric was defined to capture the degree of coupling between components in a system at a coarse level. This metric is similar to the coupling between objects (CBO) metric as defined in [12]; however, instead of counting coupling at a class level, CBM is calculated at the component level. Components with high CBM values are potential areas for maintenance problems or signs of system degeneration. While having a few components with high CBM values may not represent a problem and may be desirable, an architecture that contains many components with high CBM values indicates a poorly structured system. In such a system, the components are highly interrelated, and a change to one component likely will affect many components of the system.

To capture the level of coupling at a finer level, the metric CBMC was defined. While CBM calculates coupling at the component level, this metric is used to measure the number of classes involved in the coupling between modules. As with the CBM metric, a high CBMC value indicates modules that are interdependent and may represent maintenance problems or system degeneration. The CBMC value gives an indication of the "width" of the interface between the two components. If a component has a high CBM value and a high CBMC value, changes to the component most likely will be difficult due to its interrelationships with many classes in many components.

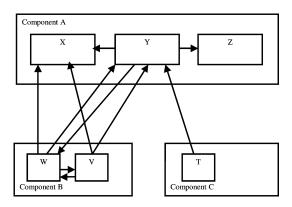

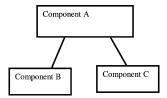

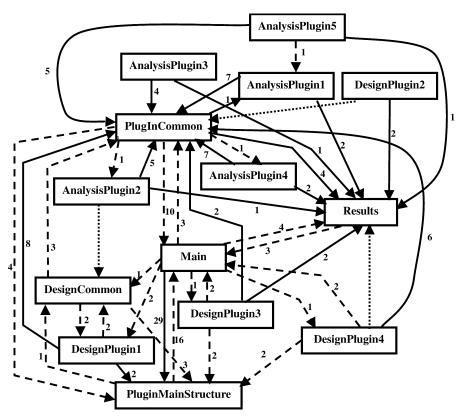

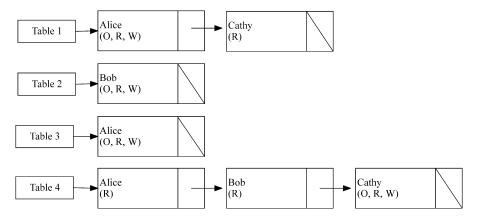

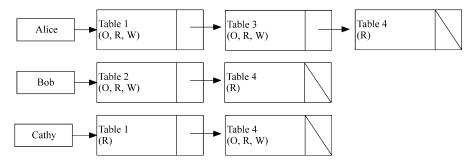

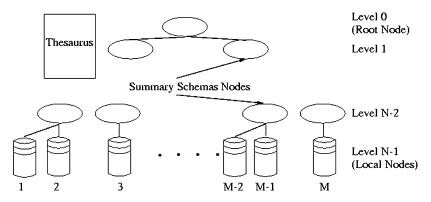

To illustrate how these metrics are calculated, consider the example of the high-level architecture of a system given in Fig. 2.

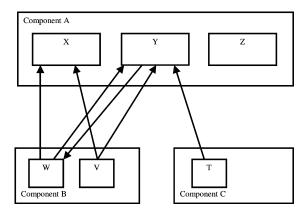

When calculating the CBM metric, the coupling among the classes of a single component is ignored. For example, the couplings between classes Y and X and Y and Z within component A are ignored in the calculation of the CBM metric value. Additionally, the direction of the coupling is ignored. Once the intra-module couplings and the direction of the couplings are ignored, the architecture of the system can be viewed as shown in Fig. 3 and the CBM values for each component can be calculated.

FIG. 2. Example diagram of a high level architecture of a system.

FIG. 3. View of example system with intra-module couplings and the direction of the couplings removed.

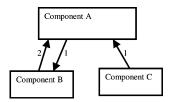

In this case, the CBM value for component A is 2 and is denoted by CBM(A) = 2. Likewise, the CBM(B) = 1 and the CBM(C) = 1.

To calculate the CBMC values for each component, the intra-module couplings are eliminated as shown in Fig. 4. Again, the direction of the arrows is ignored, but the number of classes involved is not. In this case, the CBMC value for component A is 5 and denoted by CBMC(A) = 5. Similarly, the CBMC(B) = 4 and the CBMC(B) = 2.

Retaining the direction of the coupling arrows provides another useful view of the coupling between modules and the degree of the coupling between two components along the direction of the coupling. For this view, the classes are not drawn in the diagram, but each directed arrow is labeled with the number of classes involved in the coupling along the direction of the arrow. The example system with labeled directed arrows is depicted in Fig. 5. This view is useful for determining the width of the interface between two components. In the example system, for instance, the coupling from component *C* to component *A* is narrow since only one class within component *A* is being accessed by component *C*. By looking at this view of the ar-

FIG. 4. Example system with intra-module couplings eliminated.

FIG. 5. Example system with direction of coupling included. The label represents the number of classes being accessed in the component at the endpoint of the arrow.

chitecture, components with wide interfaces (i.e., the arrows with large labels) can be identified easily.

# 5.3 Representing the Architecture

In both case studies, the same representation was used for the architecture of the systems. Boxes are used to represent high-level components of the system. Each high-level component box represents a group of Java classes in these cases. Because of the metrics used for these studies, arrows are used to represent the coupling relationships among the components of the system.

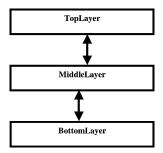

For the planned architecture, the boxes and directional arrows are defined based on the architectural styles, design patterns, and guidelines identified. For example, if the system used a layered architecture, the representation of the planned architecture might include component boxes for each layer with arrows going from one layer to the next.

Figure 6 shows a simple example of how the guidelines for a layered architecture might be translated into a representation of the planned architecture. In this example, there are three components (i.e., TopLayer, MiddleLayer, and BottomLayer). The classes within each layer are expected to communicate only with those layers that are immediately adjacent to the layer. For the case studies presented here, this planned architectural diagram was translated into a text file. The text file representation of the planned architecture shown in Fig. 6 is shown in Table I. The first line of the text file gives a name to the diagram. The subsequent lines define a component and the components that are expected to communicate with the defined component.

The representation of the actual architecture used in the case studies is derived from the source code. A parser is used to extract static coupling information (as described in the previous subsection) from the source code of the system. The output of the parser is a comma-separated file that is used to create the diagrams representing the actual architecture of the system. Each line contains coupling information including the From Subsystem, From Component, From Class, To Subsystem, To Component, To Class. An example of a subset of the output from the parser is shown in Table II.

To create the diagrams of the actual architecture from this file, the From Component and the To Component fields are used. A box is drawn for each component. When the From Component field differs from the To Component field, an arrow

FIG. 6. Example representation of a planned architecture.

# TABLE I A TEXT FILE REPRESENTATION OF THE PLANNED ARCHITECTURE SHOWN IN FIG. 6

Layered;

TopLayer:MiddleLayer;

MiddleLayer:TopLayer,BottomLayer;

BottomLayer:MiddleLayer;

| From<br>Subsys-<br>tem | From<br>Component | From<br>Class    | To<br>Subsys-<br>tem | To<br>Component | To<br>Class      |

|------------------------|-------------------|------------------|----------------------|-----------------|------------------|

| Client                 | Cache             | CacheObject      | Client               | Mediator        | Mediator         |

| Client                 | Connector         | ServletProxy     | Client               | Mediator        | Mediator         |

| Client                 | Editor            | EditorObject     | Client               | Mediator        | MediatorObject   |

| Client                 | Editor            | EditorObject     | Client               | Mediator        | Mediator         |

| Client                 | Editor            | EditorObject     | Client               | Editor          | PackageTypeSetup |

| Client                 | Editor            | EditorObject     | Client               | Editor          | Hyperwave        |

| Client                 | Editor            | PackageTypeSetup | Client               | Editor          | EditorObject     |

| Client                 | Logger            | EMSLogger        | Client               | Mediator        | MediatorObject   |

| Client                 | Logger            | EMSLogger        | Client               | Mediator        | Mediator         |

$\label{thm:table II} \textbf{Sample Output of the Actual Architecture from the Parser}$

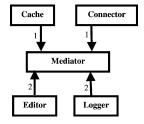

FIG. 7. Diagram of actual architecture based on partial subset of data shown in Table II.

is drawn from the box representing the From Component to the box representing the To Component. The number labels for the edges are computed by counting the number of distinct classes in the To Component reached from the From Component. The subset of information shown in Table II would lead to the diagram of the actual architecture shown in Fig. 7.

# 5.4 Case Study 1—the VQI

The implementation-oriented software architectural evaluation process was originally developed and used to evaluate several versions of the FC-MD system as described previously. As the VQI system was restructured and evolved, architectural evaluations were conducted to confirm that the actual system changes had been implemented as planned.

Version

Size (LOC including comments)

VQI1

17,522

VQI2

24,269

VQI3

26,915

VOI4

27,072

$\label{eq:Table III} \textbf{Size Characteristics of VQI}$

# 5.4.1 Background

The architectural evaluation process was used on three iterations of the VQI system. The versions of the VQI system are numbered VQI1–VQI4 indicating the order in which they were developed. Size characteristics for each version are presented in Table III.

Initially, the VQI was developed by two people and amounted to about 17K lines of commented source code (LOC) written in Java. VQI2 represents a significant architectural change from VQI1 due to maintainability problems with the previous version. The VQI2 system contains over 24K lines of commented Java source code developed by four local developers plus a team of three developers in Brazil.

VQI3 represents the work done by one developer to implement a specific task. VQI3 also represents a major change to the system in terms of increased usability and new capabilities and was released to end-users. Examples of changes in version three include converting VQI to run as both a desktop and a web application; connecting and drawing data from several different data sources instead of a single data source; and adding several advanced graphical and statistical analysis features.

VQI4 is a version of the system that is a result of an effort to eliminate the set of detected architectural violations in VQI3. The difference between VQI3 and VQI4 is relatively limited. No new features were added to this version of the system. VQI4 represents the system after changes were made specifically to correct architectural deviations.

# 5.4.2 Planned Architecture

5.4.2.1 Architectural Style. The overall architectural style of the VQI2–VQI4 versions is an Internet-based and client-server system with most of the functionality and maintenance efforts residing in the client. The server is responsible only for handling requests from the client. When the client requests data from the server, the server connects to a database, retrieves the requested data, processes it and sends the data back to the client. The client consists of the majority of the code that im-

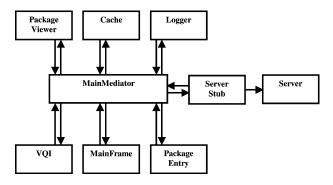

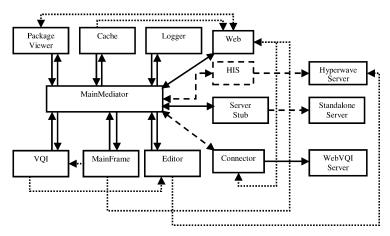

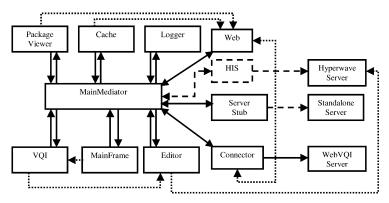

FIG. 8. A diagram of the planned architectural design for VQI2.

plements most of the functionality of VQI2–VQI4. Figure 8 shows a diagram of the planned architecture for VQI2.

## *5.4.2.2 Design Pattern.* The core of the architecture for client of VQI2–VQI4 is based on the mediator design pattern [19].

The mediator is one of the behavioral patterns described in [19]. The pattern encapsulates how a set of objects interact, providing loose coupling among the objects where the objects do not reference each other explicitly. The pattern consists of a Mediator object and Colleague objects. The Colleague objects are not aware of each other and only share information with each other through the Mediator object. The Mediator object is responsible for coordinating the communications among all of its Colleagues.

In the client side of VQI2–VQI4, the mediator design pattern is abstracted to a component level. The Mediator is a component of classes and interfaces related to controlling the communication among Colleague components. The Colleague components implement different functionalities in the client and interact with each other only through the classes of the Mediator component. In each of the Colleague components, only one class is supposed to interact with the Mediator component directly. The Server Stub component is the Colleague that handles the communication with the Server. Hence, it has interactions with the Mediator component and the Server component.

## 5.4.3 Guidelines

A set of design guidelines for the VQI was derived based on the properties of intra-module coupling, the client-server architectural style and the mediator design

pattern. The following guidelines represent sample design guidelines that are specific to the VQI system:

- [DG2] The Server should contain no references to the Client (since the server does not initiate communication with the clients).

- [DG6] The Mediator should be coupled with exactly one class per component and vice versa.

- DG2 is an example of an architectural style guideline, based on the client-server architectural style. DG6 is an example of a design pattern guideline reflecting how the mediator design pattern should appear in the implementation. The details of the metrics defined during these evaluations and a complete set of guidelines are described in [6] and [7].

#### 5.4.4 Results from the VQI2 Evaluation

The architectural evaluation of the changes implemented in VQI2 was the first iteration through the evaluation process. During this iteration, many of the guidelines, metrics and tools used in future iterations were developed. Since VQI1 was a research prototype with no official design document, the existing architecture had to be recovered and a planned design had to be created before the implementation of VQI2. When the time came for the analysis team to perform the architectural evaluation, the high-level planned design for VQI2 was readily available. Having this high-level design document allowed for a quicker evaluation. Since members of the development team were closely involved with the planned architectural design of VQI2, the expectations were to find no deviations between the planned and actual architectures.

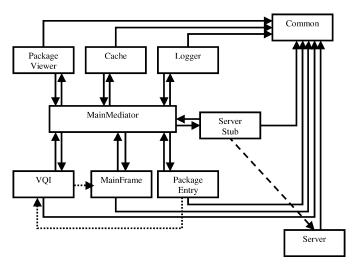

During this evaluation, a tool was developed to extract from the source code the interrelationships among components. The tool produced tables that were imported into Microsoft Excel spreadsheets and diagrams of the actual architecture were constructed manually. Figure 8 shows the diagram of the planned design for VQI2. Figure 9 shows the actual design for VQI2 that was constructed manually based on the spreadsheets generated by the tool. These diagrams were used to identify violations of the architectural design guidelines. The first iteration through the evaluation process took several weeks to conduct because new metrics and guidelines based on the architectural style and design patterns of the VQI were developed.

Although the expectations were to find no deviations, the architectural evaluation surprisingly uncovered four architectural violations during the first iteration. Three of the violations can be seen in comparison diagram (Fig. 9). The fourth violation was a metric guideline violation. The violation from the PackageEntry component to the VQI component was a design pattern guideline violation and was considered to

FIG. 9. A diagram of the actual architecture of VQI2. Extra coupling violations are shown with dotted lines. Missing coupling violations are shown with dashed lines.

be serious. The other violations were considered to be minor; however, one resulted in a change to the original metric guidelines.

From this iteration of the evaluation process, several resources were created for future versions of the VQI and for future iterations through the evaluation process. These resources include a set of metrics, architectural guidelines, and a diagram of the planned architecture. In addition to the VQI-specific resources, the first iteration of the process also resulted in the creation of a tool to extract the static coupling information from the source code. Although the first evaluation took several weeks to perform, the metrics, guidelines, and tool support enabled faster evaluations of new versions of the VQI system.

This first iteration through the evaluation process provided several lessons. Having members of the design team participate in the development does not necessarily prevent the occurrence of serious architectural violations. In this case, the main objective of the development was to re-engineer the system into a more maintainable state. Developers actively participated in the re-design of the architecture of the system. Architectural mismatches were not expected in the actual implementation, yet they still occurred.

The experiences from this iteration indicate that implementing design patterns may not be entirely straightforward. The goals of the architectural design and the implementation details of the design pattern were explained to the developers. Still, design pattern violations appeared in the implementation. Although it is believed

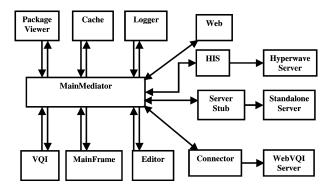

FIG. 10. A diagram of the planned architectural design for VQI3 and VQI4.

that the mediator design pattern has and will continue to make the VQI system easier to maintain, when new developers are introduced to the concept, understanding the implementation details of the design pattern has a learning curve.

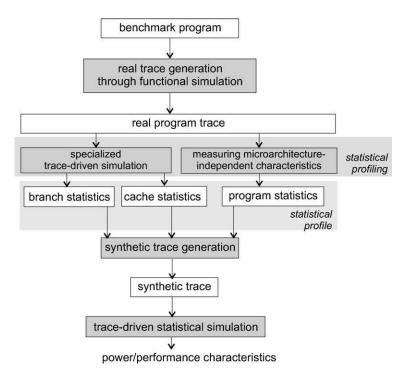

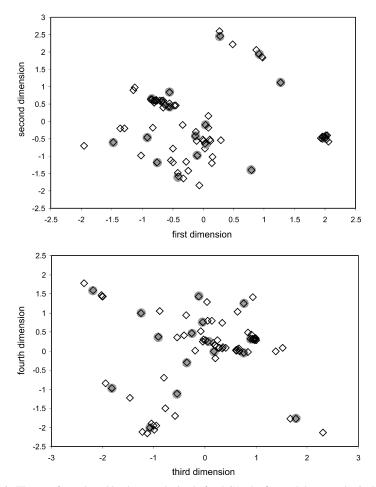

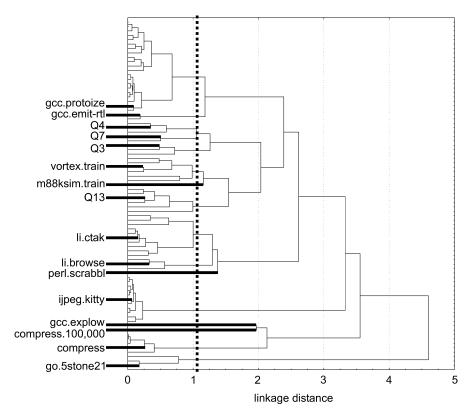

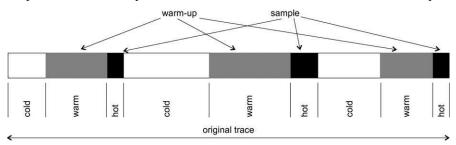

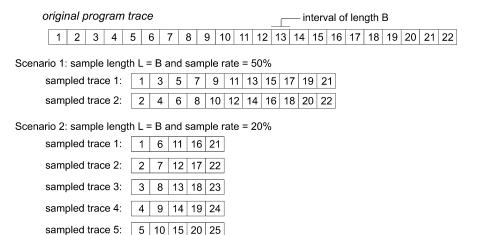

#### 5.4.5 Results from the VQI3 Evaluation