# THE e HARDWARE VERIFICATION LANGUAGE

#### Sasan Iman Sunita Joshi

## The *e* Hardware Verification Language

### The *e* Hardware Verification Language

Sasan Iman

SiMantis Inc. Santa Clara, CA

Sunita Joshi

SiMantis Inc. Santa Clara, CA

KLUWER ACADEMIC PUBLISHERS NEW YORK, BOSTON, DORDRECHT, LONDON, MOSCOW eBook ISBN: 1-4020-8024-7 Print ISBN: 1-4020-8023-9

©2004 Springer Science + Business Media, Inc.

Print ©2004 Kluwer Academic Publishers Boston

All rights reserved

No part of this eBook may be reproduced or transmitted in any form or by any means, electronic, mechanical, recording, or otherwise, without written consent from the Publisher

Created in the United States of America

Visit Springer's eBookstore at: and the Springer Global Website Online at: http://www.ebooks.kluweronline.com http://www.springeronline.com To our loving families

# Table of Contents

| Table of Contents                                                                                                                                                 | vii                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Reader Feedback                                                                                                                                                   | xvii                                                                                   |

| Foreword                                                                                                                                                          | xix                                                                                    |

| Preface                                                                                                                                                           | xxi                                                                                    |

| Chapter 1: Introduction<br>1.1 Design of e<br>1.2 Learning e<br>1.3 Programming in e<br>1.4 Book Structure<br>1.5 Book Conventions and Visual Cues<br>1.6 Summary | 1<br>2<br>4<br>5<br>6                                                                  |

| Part 1: Verification Methodologies and Environment Architecture                                                                                                   | 9                                                                                      |

| Chapter 2: Verification Methodologies                                                                                                                             | 12            13            14            16            18            18            19 |

| <ul> <li>2.2.3 Effectiveness</li> <li>2.2.4 Completeness</li> <li>2.2.5 Verification Environment Reusability</li> <li>2.2.6 Simulation Result Reusability</li> <li>2.3 Directed Test Based Verification</li> <li>2.3.1 Task Driven Verification Methodology</li> <li>2.3.2 Verification Quality</li> <li>2.4 Constrained Random Test Based Verification</li> <li>2.4.1 Random Based Verification and Practical Considerations</li> <li>2.5 Coverage Driven Verification</li> <li>2.5.1 Verification Quality</li> <li>2.6 The Enabling Technology: Hardware Verification Languages</li> <li>2.7 Summary</li> </ul>                                                                                          | 20<br>20<br>21<br>22<br>23<br>23<br>24<br>26<br>27<br>29<br>29<br>29             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

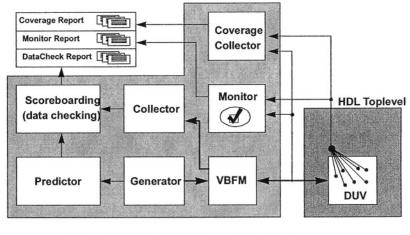

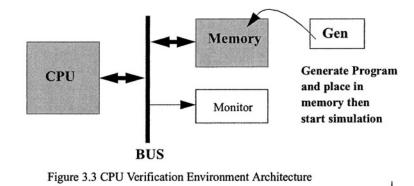

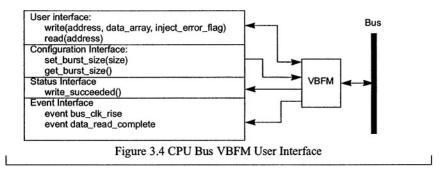

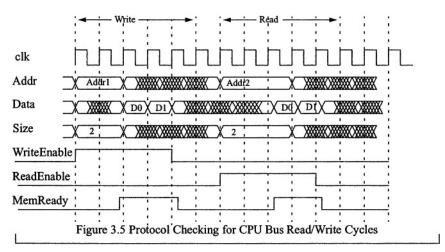

| <ul> <li>3.1.1 Simulation Goals</li> <li>3.1.2 Verification Views</li> <li>3.1.3 Verification Checks</li> <li>3.1.4 Debugging and the Verification Plan</li> <li>3.2 Verification Environment Architecture</li> <li>3.2.1 CPU Verification</li> <li>3.2.2 Verification Bus Functional Model</li> <li>3.2.2.1 BFM Features</li> <li>3.2.2.2 VBFM User Interface</li> <li>3.2.3 Verification Environment Initialization</li> <li>3.2.3.1 Verification Environment Configuration</li> <li>3.2.3.2 Verification Environment Configuration</li> <li>3.2.3 Data and Scenario Generation</li> <li>3.2.4 Monitors</li> <li>3.2.5 Data Collector</li> <li>3.3 Module Level vs. System Level Verification</li> </ul> | 32<br>33<br>34<br>35<br>37<br>38<br>39<br>40<br>41<br>41<br>42<br>43<br>45<br>46 |

| Part 2: All About e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51                                                                               |

| Chapter 4: e as a Programming Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53                                                                               |

| hapter 4: e as a Programming Language        | 53   |

|----------------------------------------------|------|

| 4.1 e Programming Paradigm                   |      |

| 4.1.1 Declarative Programming                | . 54 |

| 4.1.2 Aspect-Oriented Programming            |      |

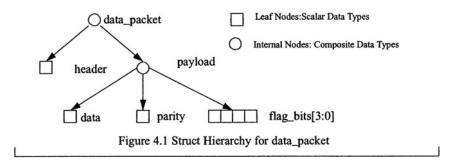

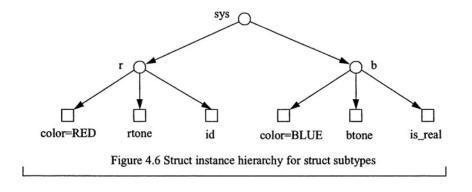

| 4.2 Struct and the Struct Instance Hierarchy |      |

| 4.2.1 Data References                        | . 58 |

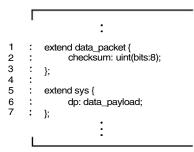

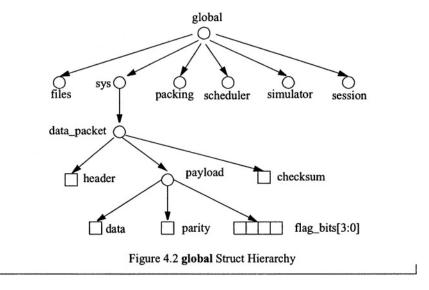

| 4.2.2 global and sys                         | . 58 |

|                                              |      |

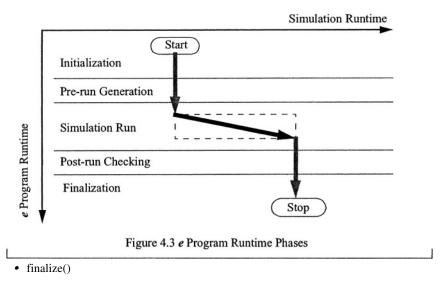

| 4.3 Execution Flow                            |

|-----------------------------------------------|

| 4.3.2 Steps to Writing an e Program           |

| 4.4 Structure of an e Program                 |

| 4.4.1 Lexical Conventions                     |

| 4.4.2 Code Segments                           |

| 4.4.3 Comments                                |

| 4.5 Statements                                |

| 4.5.1 Import statements                       |

| 4.5.1.1 Import Order Dependency               |

| 4.5.2 struct Declaration Statement            |

| 4.5.2.1 Struct Data Members                   |

| 4.5.2.2 Methods                               |

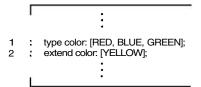

| 4.5.3 Type and Subtype Declaration Statements |

| 4.5.3.1 Enumerated Type Declarations          |

| 4.5.3.2 Scalar Subtype Declarations           |

| 4.5.3.3 Struct Subtype Declarations           |

| 4.5.4 Extension Statements                    |

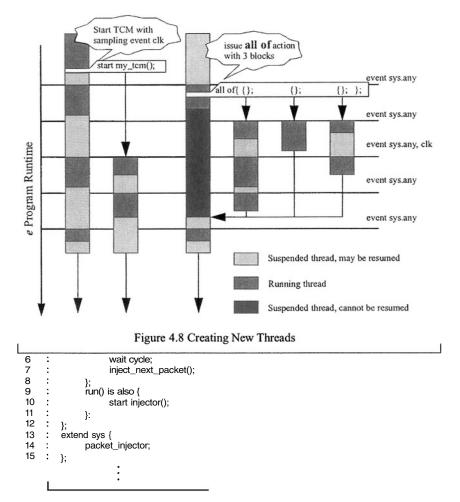

| 4.6 Concurrency and Threads                   |

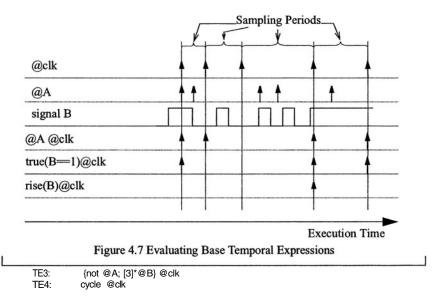

| 4.6.1 Events and Temporal Expressions         |

| 4.6.1.1 Temporal Expressions                  |

| 4.6.2 Time Consuming Methods (TCMs)           |

| 4.6.3 Thread Control                          |

| 4.6.4 Semaphores                              |

| 4.6.4.1 Mutual Exclusion                      |

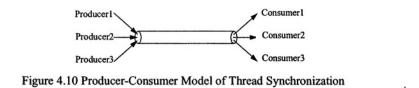

| 4.6.4.2 Thread Synchronization                |

| 4.7 Summary                                   |

| Chapter 5: e as a Verification Language81     |

| 5.1 Constrained Random Generation 82          |

| 5.1.1 Random Generation                       |

| 5.1.2 Generation Constraints                  |

| 5.1.3 Pre-Run vs. On-the-Fly Generation       |

| 5.2 HDL Simulator Interface                   |

| 5.2.1 Multi-Valued Logic 89                   |

| 5.3 HDL Simulator Synchronization             |

| 5.3.1 Notion of Time 90                       |

| 5.4 Units                                     |

| 5.5 e-Ports                                   |

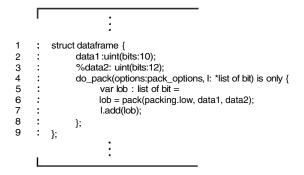

| 5.6 Packing and Unpacking 94                  |

| 5.6.1 Packing                                 |

| 5.6.2 Unpacking 97                            |

| 5.7 Coverage                                  |

| 5.8 Summary                                   |

|                                               |

| Part 3: | Topology and Stimulus Generation                 | 103        |

|---------|--------------------------------------------------|------------|

|         | 6: Generator Operation                           |            |

| 6.1     | Generator Execution Flow                         | 105        |

|         | 6.1.1 pre_generate()                             | 106<br>107 |

| 60      | 6.1.2 post_generate()                            | 107        |

| 63      | Constraint Types                                 | 100        |

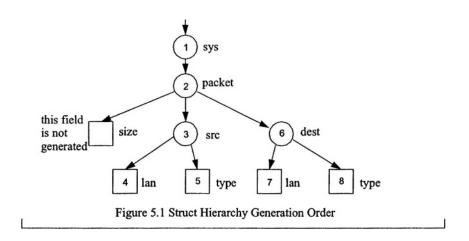

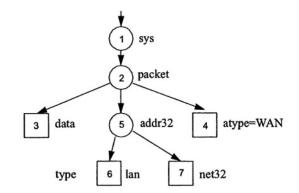

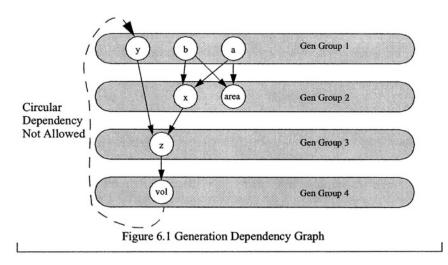

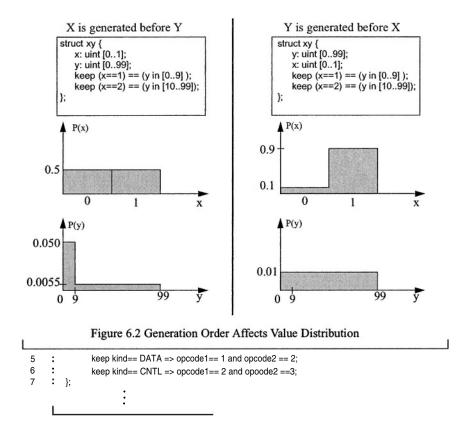

| 0.5     | 6.3.1 Item Generation Order                      | 109        |

|         | 6.3.2 Reduction                                  |            |

|         | 6.3.3 Constraint Evaluation                      |            |

|         | 6.3.4 Set-Scalar                                 | 112        |

| 6.4     | Controlling the Generation Order                 | 112        |

| ••••    | 6.4.1 when Blocks                                | 114        |

|         | 6.4.2 Explicit Order Definition                  | 114        |

|         | 6.4.3 value()                                    | 114        |

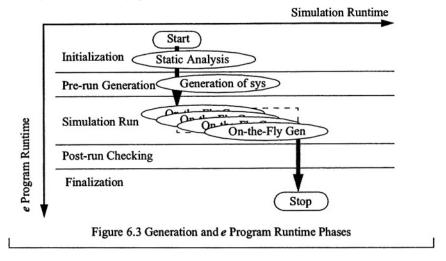

| 6.5     | Generation and Program Execution Flow            | 115        |

|         | 6.5.1 Static Analysis                            | 115        |

|         | 6.5.2 On-the-Fly Generation                      | 116        |

|         |                                                  | 116        |

|         | 6.5.2.2 Data Generation: gen                     | 118        |

| 6.6     | Summary                                          | 120        |

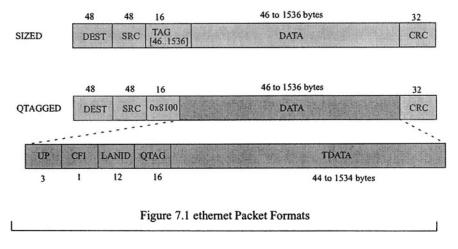

| Chapter | 7: Data Modeling and Stimulus Generation         | 121        |

|         |                                                  | 122        |

|         | 7.1.1 Physical Fields                            | 122        |

|         | 7.1.2 Determinant Fields                         | 123        |

|         |                                                  | 123        |

|         | 7.1.3.1 Avoiding Data Generation Inconsistencies |            |

| 7.2     |                                                  | 126        |

|         |                                                  | 127        |

|         |                                                  | 128        |

|         |                                                  | 128        |

| 7.3     | Data Abstraction Translation                     |            |

|         | 7.3.1 Packing: Logical View to Physical View     |            |

|         |                                                  | 131        |

|         |                                                  | 131        |

| 74      | 7.3.2.2 Subtypes                                 | 133        |

| 7.4     |                                                  | 134        |

|         |                                                  | 135        |

|         | 7.4.2 Coordinated Ranges                         |            |

| 75      |                                                  |            |

| 1.0     | Summary                                          | 136        |

|         | Summary                                          | 136        |

|                                                                   | 400        |

|-------------------------------------------------------------------|------------|

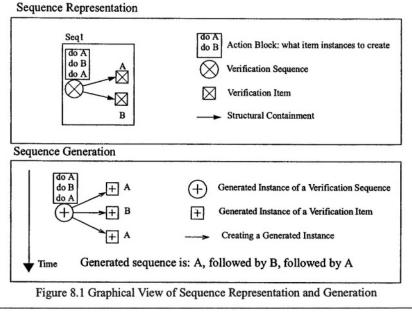

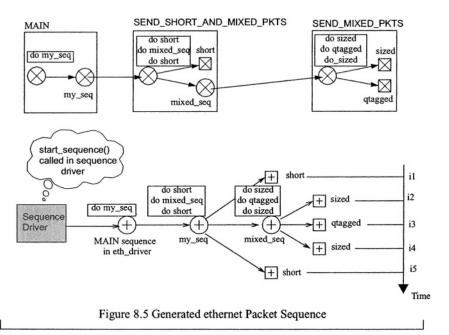

| 8.1 Verification Scenarios as Sequences                           |            |

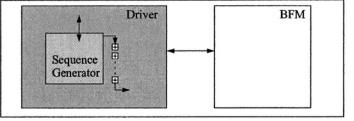

| 8.2 Sequence Generation Architecture                              | 140        |

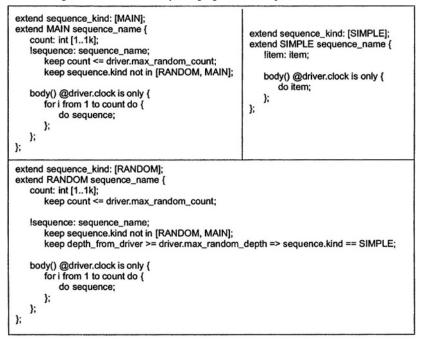

| 8.3 Homogeneous Sequences                                         | 142        |

| 8.3.1 Verification Environment Enclosing a Sequence Generator     | 143        |

| 8.3.2 Verification Item Definition                                | 144        |

| 8.3.3 Driver and Sequence Creation                                |            |

| 8.3.4 Verification Environment Attachment                         | 145        |

| 8.3.5 User Defined Sequences                                      |            |

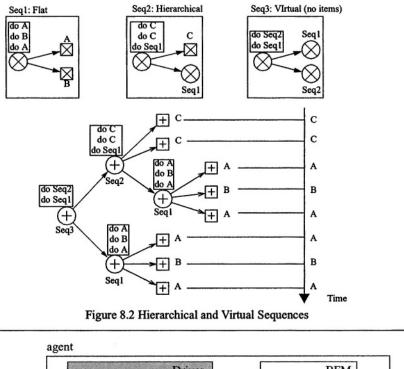

| 8.3.5.1 Flat Sequences                                            | 146        |

| 8.3.5.2 Hierarchical Sequences                                    | 147        |

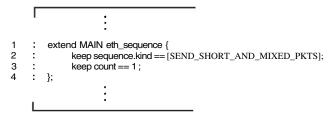

| 8.3.6 Default Sequence Generation Starting Point                  |            |

| 8.3.6.1 Merging New Sequence Kind with the Default Start Point    | 149        |

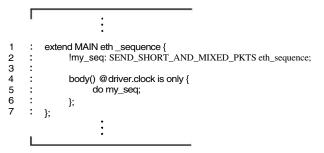

| 8.3.6.2 Over-riding the Default Start Point to a New Sequence Kir |            |

|                                                                   |            |

| 8.3.7 Sequence Generator Flow Customization                       |            |

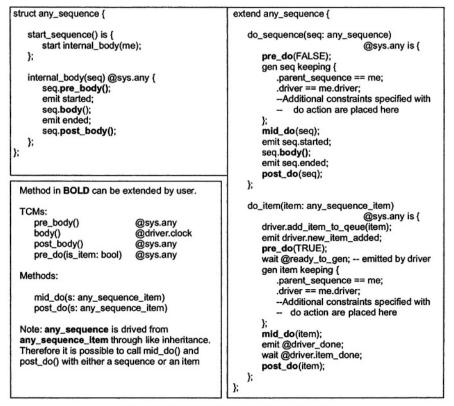

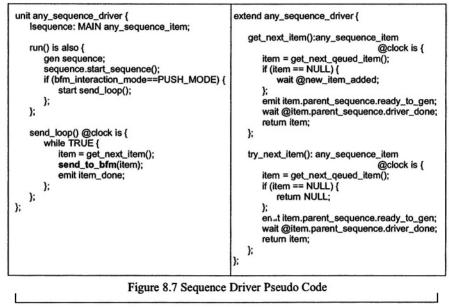

| 8.4 Sequence Synchronization                                      | 151        |

| 8.4.1 Sequence and Sequence Driver Interaction                    | 152        |

| 8.4.1.1 Push Mode                                                 | 153        |

| 8.4.1.2 Pull Mode                                                 | 154        |

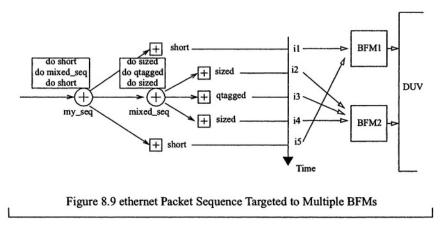

| 8.4.2 Multiple Sequence Synchronization                           |            |

|                                                                   | 104        |

|                                                                   |            |

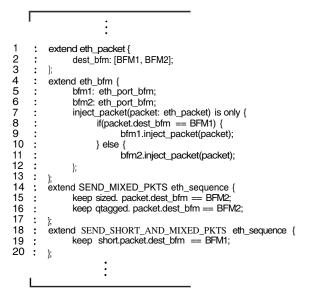

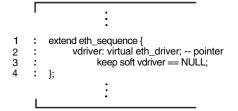

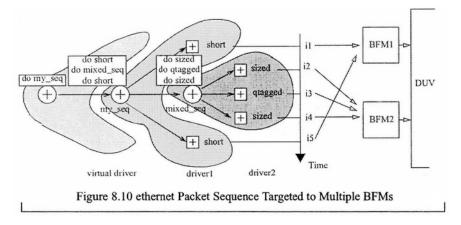

| 8.5 Heterogeneous Sequences                                       | 155        |

| 8.5 Heterogeneous Sequences                                       | 155<br>155 |

| 8.5 Heterogeneous Sequences                                       | 155<br>155 |

| Part 4: Response Collection, Data Checking, and Property Monitoring | 163        |

|---------------------------------------------------------------------|------------|

| a shire a filler filler a s                                         | 165<br>165 |

|                                                                     | 167        |

|                                                                     | 167        |

|                                                                     | 169        |

|                                                                     | 170        |

| •                                                                   | 171        |

|                                                                     | 172        |

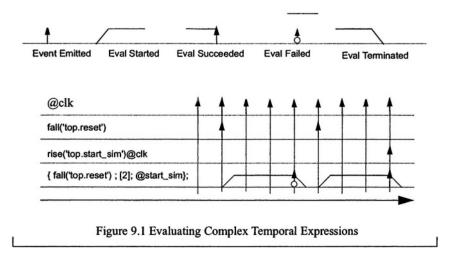

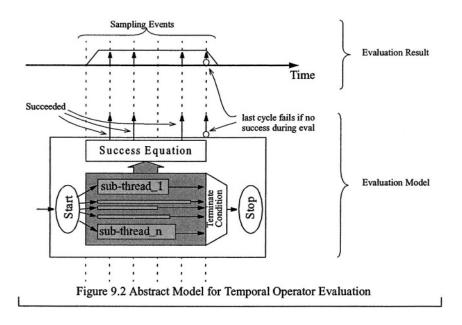

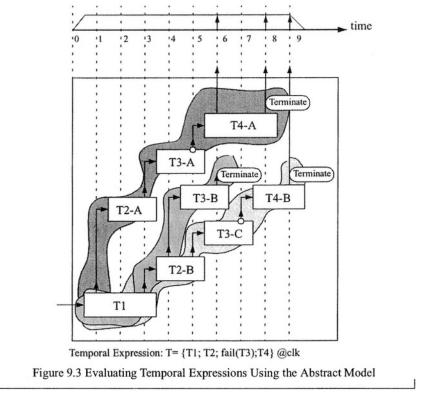

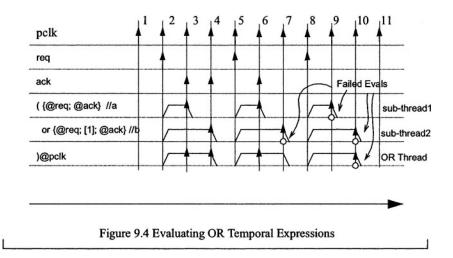

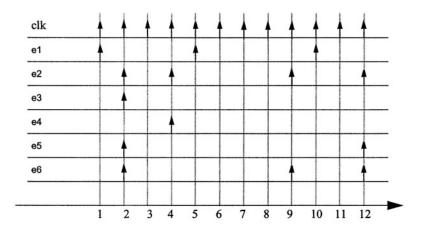

| 9.3 Temporal Operators                                              | 172        |

| 9.3.1 Base Temporal Operators                                       | 173        |

| 9.3.2 Atomic Temporal Operators                                     | 173        |

| 9.3.2.1 fail                                                        | 173        |

|                                                                     | 173        |

|                                                                     | 174        |

|                                                                     | 175        |

|                                                                     | 176        |

|                                                                     | 176        |

| 9.3.3.2 Fixed Repetition                                            | 176        |

| <ul> <li>9.3.3.3 True Match Variable Repeat</li> <li>9.3.3.4 Yield</li> <li>9.3.3.5 eventually</li> <li>9.4 Temporal Operator Arithmetic</li> <li>9.5 Temporals Dictionary</li> <li>9.5.1 English Phrases and event Definitions</li> <li>9.5.2 English Phrases and Property Checking:</li> <li>9.6 Performance Issues</li> <li>9.6.1 Over-sampling</li> <li>9.6.2 Missing Sampling Event</li> <li>9.6.3 Unanchored Sequences</li> <li>9.6.4 Nested Sampling</li> <li>9.7 Summary</li> </ul> | 177<br>177<br>177<br>179<br>179<br>183<br>183                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Chapter 10: Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 190<br>191<br>192<br>193<br>193<br>193<br>194<br>194                                           |

| Chapter 11: Collectors and Monitors                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 199<br>201<br>202<br>203<br>203<br>204<br>204<br>204<br>205<br>205<br>205<br>205<br>207<br>208 |

| 11.3.2 Event Extraction                         |     |

|-------------------------------------------------|-----|

| 11.3.3 Reporting 2                              | 210 |

| 11.3.3.1 Messages                               | 210 |

| 11.3.3.2 Message Loggers 2                      | 210 |

|                                                 | 211 |

| Chapter 12: Scoreboarding                       | 213 |

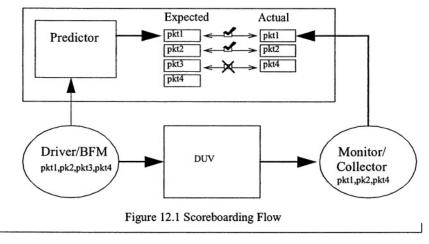

| 12.1 Scoreboard Implementation 2                | 214 |

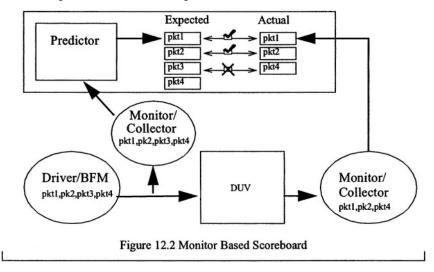

| 12.2 Scoreboard Configuration Types 2           | 215 |

| 12.2.1 Driver/BFM Based Scoreboard 2            | 216 |

| 12.2.2 Monitor Based Scoreboard 2               | 216 |

| 12.3 Attaching Scoreboards to the Environment 2 | 217 |

| 12.3.1 Direct Method Call 2                     | 217 |

| 12.3.2 Using Hook Methods 2                     |     |

| 12.3.3 Using Events 2                           |     |

| 12.4 Scoreboarding Strategies 2                 |     |

| 12.4.1 End-to-end Scoreboarding 2               |     |

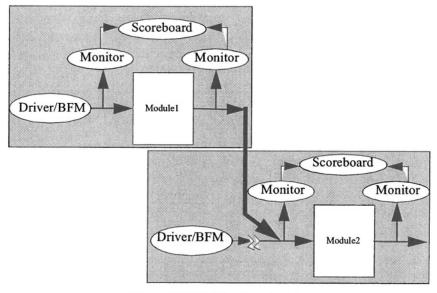

| 12.4.2 Multistep Scoreboarding 2                |     |

| 12.5 Summary                                    |     |

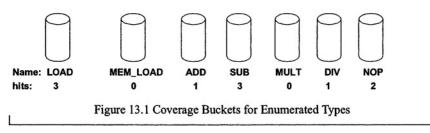

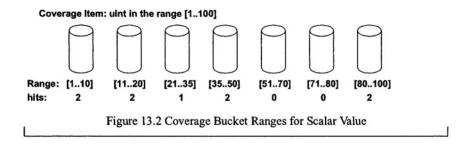

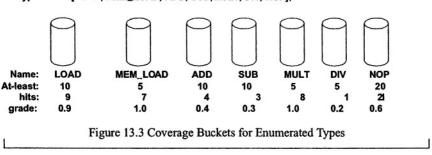

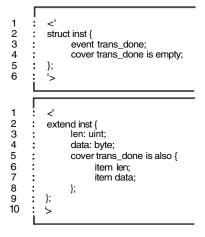

Part 5: Coverage Modeling and Measurement 223 13.1 Coverage Collection Steps ..... 225 13.2 Coverage Terminologies ..... 226 13.3 Scalar Coverage Constructs ..... 227 13.3.2 Basic Coverage Items ..... 229 13.3.3 Sampling Events ..... 231 13.3.4.1 Bucket Ranges ..... 233 13.3.4.2 Default Buckets ..... 235 13.3.4.3 Illegal Buckets ..... 235 13.3.4.4 Ignored Buckets ...... 236 13.3.4.5 Bucket Grading ..... 236 13.4 Composite Coverage Items ..... 236 13.4.1 Cross Coverage Items ..... 237 13.4.2 Transition Coverage Items ..... 238 13.5.1 Coverage Group Extension ..... 240 13.5.2 Coverage Item Extension ..... 240

| 14.1 Coverage Planning and Design          | 246 |

|--------------------------------------------|-----|

| 14.2 Coverage Implementation               |     |

|                                            |     |

| 14.2.1 Coverage Model Organization         |     |

| 14.2.1.1 Hierarchical Coverage Models      | 248 |

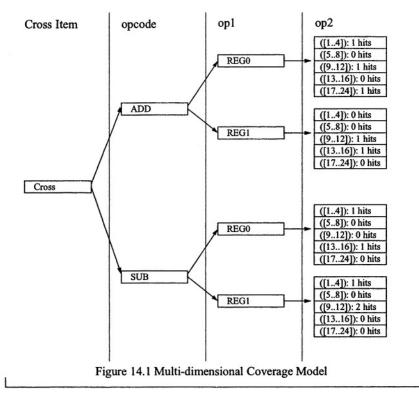

| 14.2.1.2 Multi-dimensional Coverage Models | 250 |

| 14.2.2 Coverage Data Source                | 251 |

| 14.2.2.1 DUV Signal Coverage               |     |

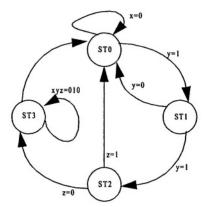

| 14.2.2.2 State Machine Coverage            | 253 |

| 14.2.2.3 Coverage of Generated Data        | 255 |

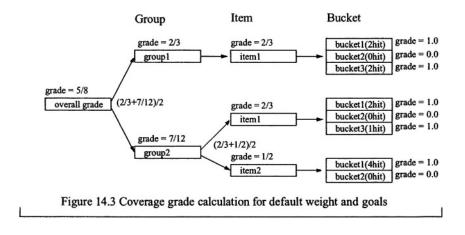

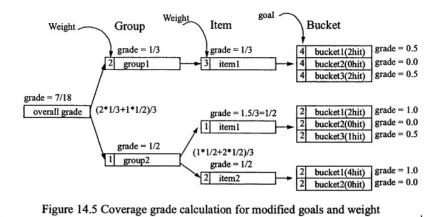

| 14.3 Coverage Grading                      | 256 |

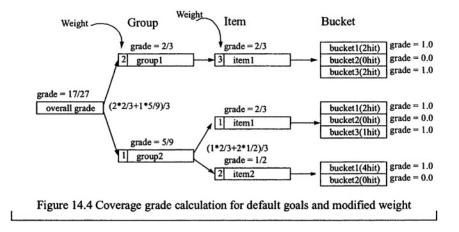

| 14.3.1 Changing Default Weights            | 258 |

| 14.3.2 Changing Default Goals              |     |

| 14.3.3 Ungradeable Items                   |     |

| 14.3.4 Illegal and Ignored Items           | 261 |

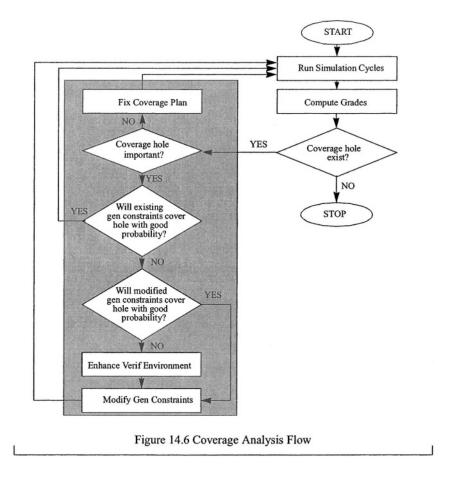

| 14.4 Coverage Analysis                     | 261 |

| 14.5 Summary                               |     |

#### Part 6: e Code Reuse

265

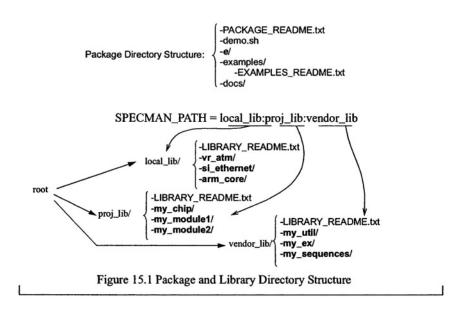

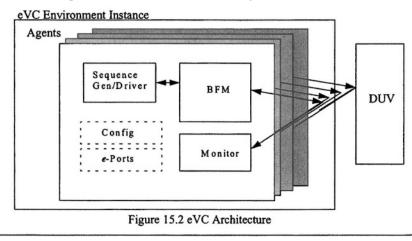

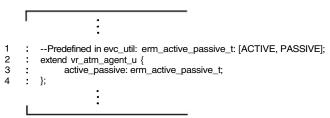

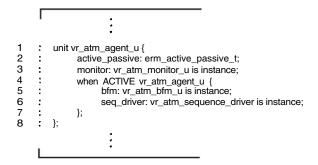

| Chapter 15: e Reuse Methodology       2         15.1 eVCs: e Verification Components       2         15.2 Packages and Package Libraries       2         15.2.1 Naming Conventions       2         15.2.2 Directory Structure       2         15.2.3 Accessing Files       2         15.2.4 LIBRARY_README.txt File       2         15.2.5 PACKAGE_README.txt File       2         15.2.6 any_env unit       2 | 268<br>269<br>270<br>271<br>272<br>273<br>273<br>273        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 15.3 Features       2         15.3.1 eVC Environment       2         15.3.2 eVC Agents       2         15.3.3 Configuration Settings       2         15.3.4 Sequence Generator and Driver       2         15.3.5 e-Port Interface       2         15.3.6 BFM       2         15.3.7 Monitor       2         15.4 Summary       2                                                                               | 274<br>276<br>276<br>277<br>277<br>277<br>277<br>277<br>277 |

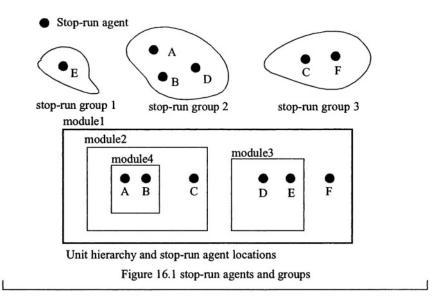

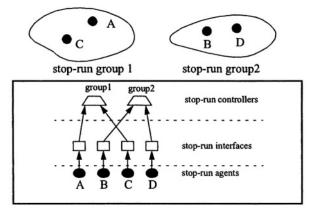

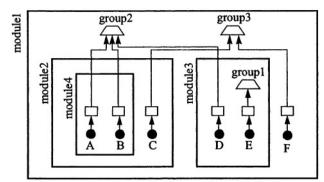

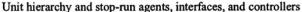

| Chapter 16: si_util Package       2         16.1 Stop-Run Controller       2         16.1.1 Stop-Run Controller and Stop-Run Interface       2         16.1.2 Migrating to Using Stop-Run Interfaces       2         16.1.3 Multiple Stop-Run Groups in the Same Module       2         16.1.4 Multiple Stop-Run Groups across the Hierarchy       2                                                           | 280<br>281<br>281<br>281<br>283                             |

| 16.1.5 Modular Stop-Run Control         | 286 |

|-----------------------------------------|-----|

| 16.2 Memory Package                     |     |

| 16.2.1 si_util_mem_mgr Memory Manager   | 288 |

| 16.2.1.1 Memory Segment Placement Style | 290 |

| 16.2.2 si_util_mem Sparse e Memory Core | 291 |

| 16.3 Native e Time Manager              | 293 |

| 16.4 Signal Generator                   | 295 |

| 16.5 Native e Float Arithmetic Package  | 299 |

| 16.6 Summary                            | 301 |

#### Part 7: Appendices

303

| e BNF Grammar 305 |  |

|-------------------|--|

|-------------------|--|

| e | Reserved | Keywords | 331 |

|---|----------|----------|-----|

|---|----------|----------|-----|

| eRM Compliance Checks 333<br>C.1 Packaging and Name Space Compliance Checks<br>C.2 Architecture Compliance Checks<br>C.3 Reset Compliance Checks<br>C.4 Checking Compliance Checks<br>C.5 Coverage Compliance Checks | 336<br>336<br>338 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| C.4 Checking Compliance Checks                                                                                                                                                                                       | 338               |

| C.6 Sequences Compliance Checks                                                                                                                                                                                      | 339               |

| C.7 Messaging Compliance Checks                                                                                                                                                                                      |                   |

| C.9 Documentation Compliance Checks                                                                                                                                                                                  | 340               |

| C.10 General Deliverables Compliance Checks<br>C.11 End of Test Compliance Checks                                                                                                                                    |                   |

| Index                                                                                                                                                                                                                | 343               |

## Reader Feedback

Functional verification is a dynamic and fast growing field where verification methodologies are continuously enhanced and improved. At the same time, the e language is in the process of being adopted as IEEE standard 1647 where its syntactical and semantic features will be summarized and detailed in a language reference manual. In consideration of these dynamics, this book will continue to be updated to reflect the ongoing events in the verification community. We encourage you, as the reader, to help enhance this book by sending us your feedback on topics that you feel should be explained more concisely or more clearly; and we welcome comments on errors or inconsistencies that we may have overlooked in this first edition. Please send us your feedback via E-mail to **theehvl@simantis.com**.

## Foreword

I am glad to see this new book on the e language and on verification. I am especially glad to see a description of the e Reuse Methodology (eRM). The main goal of verification is, after all, finding more bugs quicker using given resources, and verification reuse (module-to-system, old-system-to-new-system etc.) is a key enabling component.

This book offers a fresh approach in teaching the e hardware verification language within the context of coverage driven verification methodology. I hope it will help the reader understand the many important and interesting topics surrounding hardware verification.

Yoav Hollander Founder and CTO, Verisity Inc.

## Preface

This book provides a detailed coverage of the e hardware verification language (HVL), state of the art verification methodologies, and the use of e HVL as a facilitating verification tool in implementing a state of the art verification environment. It includes comprehensive descriptions of the new concepts introduced by the e language, e language syntax, and its associated semantics. This book also describes the architectural views and requirements of verification environments (randomly generated environments, coverage driven verification environments, etc.), verification blocks in the architectural views (i.e. generators, initiators, collectors, checkers, monitors, coverage definitions, etc.) and their implementations using the e HVL. Moreover, the e Reuse Methodology (eRM), the motivation for defining such a guide-line, and step-by-step instructions for building an eRM compliant e Verification Component (eVC) are also discussed.

This book is intended for a wide range of users, including junior verification engineers looking to learn basic concepts and syntax for their project, to advance users looking to enhance the effectiveness and quality of a verification environment, to developers working to build eVCs, and also as a reference work for users seeking specific information about a verification concept and its implementation using the e HVL.

#### Acknowledgements

The e hardware verification language could not have existed without the creativity, hard work, and diligence of people at Verisity Inc. Verification methodologies as discussed in this book were either created or impacted by Verisity's continuous effort to address the functional verification challenge. We are grateful to Verisity and its employees for their hard work to create e and to keep it at the leading edge of verification technologies.

In the writing of this book, we have been fortunate to be supported by great engineers and technologists who have provided us with comments, feedbacks, and reviews of the material herein. We would like to acknowledge the following individuals for their active participation in the review process: Corey Goss, Michael McNamara, Kumar Malhotra, Michael McNamara, Patrick Oury, Andrew Piziali, Al Scalise, Efrat Shneydor, Mark Strickland, and Hari Tirumalai.

Sasan Iman Sunita Joshi Santa Clara, CA

#### **CHAPTER 1**

Introduction

#### 1.1 Design of *e*

The e hardware verification language is designed to support the special requirements of functional verification. e provides abstractions that are specifically targeted to better implementations of functional verification concepts. Creating a language that provides native support for verification concepts gives the following benefits:

- Less code for engineers to write, which leads to higher productivity when implementing a verification environment

- Less code also means fewer errors in building the verification environment because the number of errors in a program is proportional to the lines of code in that program

- Greater runtime efficiency as verification abstractions are optimized in the language runtime engine

- Provides an easy interface with HDL simulators

The e programming language was created, supported, and enhanced by Verisity Inc. of Mountain View, CA. The Specman Elite® tool suite is also produced byVerisity and provides the runtime and development environments for the e language. Specman Elite provides the necessary utilities for writing, debugging, integrating, reporting, and configuring e programs. Although Specman Elite and the e language are closely tied, the e language exists independently of this runtime environment. Therefore, this book mainly focuses on verification tasks and their implementation using the e language independent of Specman Elite®. The implicit assumption is that an e program should be able to run in any runtime environment developed for the language and should not depend on specific implementations of any runtime environment. Consequently, this book does not describe Specman Elite in any detail.

As of this writing, e is in the process of standardization as IEEE P1647. The goal of this standardization process is to develop a standard verification language based on the e language, by clearly specifying:

- The *e* language constructs

- The e language interaction with standard simulation languages of interest

- The libraries currently used in conjunction with *e*

- · New features of interest

Once this process is completed, the language grammar and a language reference manual will be produced by the working group for this standard. The latest status of this standardization effort can be obtained by visiting **www.ieee1647.org**.

#### 1.2 Learning e

Programming languages are not the end but a means to more efficient implementations of concepts. We learn a new programming language not because we find new language constructs and syntaxes fascinating, but because they are useful in making us become better problem solvers. Thus, the first step in learning a new language is to understand the underlying concepts that first motivated the development of that language. These concepts are rooted in the problem that a language was created to addresses as well as the methodology that is the approach of choice for solving such problems as a conceptual level.

Functional verification is the specific problem e is designed to address. Methodologies for performing functional verification have evolved over the years in order to meet the verification demands of increasingly complex systems. Detailed understanding of the latest functional verification methodologies is essential to learning the e language.

Before a methodology can be implemented in a programming language, it has to be represented with an architectural view. This architectural view consists of components, modules, and tasks that have direct correspondence to constructs and abstractions provided in that language.

This book describes the evolution of functional verification methodologies culminating in the development of coverage driven verification methodology (chapter 2). The architectural view for effective application of this methodology and its components are described in chapter 3. As previously stated, in most cases, an architectural view is created with the specific facilities of a language in mind. In the case of e, language features and facilities were motivated by the architecture that leads to the best implementations of coverage driven verification methodology. Before learning the e language, it is important to gain a good understanding of coverage driven methodology and the architectural view for its verification environment. Such a detailed understanding promotes the learning to become an expert in using e to build a robust and complete verification environment rather than mere proficiency in the e language.

New languages are designed to support new, or a mix of new and existing programming paradigms. A programming paradigm describes the view that a programmer has of program execution. For example, in object-oriented programming, a program is viewed as a collection of communicating objects. In imperative programming, a program is viewed as a state and instructions that change this state. Learning how a new language is used is more involved than just learning the syntax of that language. A good part of becoming an expert in a programming language is understanding how to best implement the solution to a problem using the programming paradigms supported by that language. Programmers often learn the syntax of a new language only to use this new knowledge to implement a program using concepts from their previous programming language, an important step in learning C++ is to learn object-oriented programming. It is easy to learn C++ syntax and use it to write a program in the style of BASIC. But doing so would defeat the purpose behind the creation of C++ and would render learning C++ a futile effort.

Effective functional verification requires a mix of different programming paradigms. e supports imperative, object oriented, aspect oriented, and declarative programming paradigms. It is important to learn these programming paradigms and understand the proper use of utilities supporting these paradigms. Having a clear understanding of the usefulness of each paradigm to each verification task leads to a better verification program that takes full advantage of these paradigms. Chapter 4 describes e as a programming language and covers these programming paradigms.

Still, a language cannot be learned completely in a short time. Becoming an expert in a new language, its programming paradigms, and appropriate methodologies requires practice, and a conscious effort to expand beyond the subset that you know at any given time. The best approach to learning e is to focus on the verification tasks and language programming paradigms rather than the language constructs. You should start by building the smallest and most trivial verification environment on your own. I often come across verification engineers who in spite of having one or more years of experience in e, are unable to write the most basic program in e simply because their job only required them to learn a subset of the language and to work on an already existing program. Learning e is best accomplished by building a skeleton e program for a verification environment, and enhancing the components in this verification environment by learning more about how each component is designed and operated.

Functional verification has now become a major part of any design project consisting of multiple verification developers. Such developers will create code, but often also use code from other vendors or previous projects. As such, software programming concepts designed to facilitate code reuse and multiple team development efforts are an important part of building a verification environment. Solid understanding of the e Reuse Methodology (eRM) helps in building e verification components that can be reused and combined with components developed by other teams. eRM is therefore especially important in working within larger verification environment development projects.

A systematic approach to learning the *e* language includes the following steps:

#### CHAPTER 1

- Learn functional verification methodologies especially coverage driven verification.

- Understand the recommended verification environment architecture for performing coverage driven verification.

- Understand programming paradigms supported by the *e* language, and their usefulness for different verification tasks.

- Learn eRM to understand how to structure software so that it is reusable and can be used combined other independently developed modules.

- Learn to build the most basic verification environment from scratch, even if all its components have no content.

- Learn the underlying operation of different language facilities (i.e. random generation, temporal expressions, sequences, etc.). Once you know how these facilities work and what operations they support, the appropriate syntax can be referenced and remembered as you become more familiar with the language.

- Focus first on just enough syntax so that you can build a syntactically correct program to create the desired module hierarchy and method calls.

#### 1.3 Programming in e

Program development consists of 4 main stages:

- · Logistic Planning

- Analysis

- Design

- Implementation

Logistic planning is concerned with software organization issues such as directory structure, naming conventions, future plans for reuse across projects generations, etc. In the analysis stage, establish a clear understanding of the problem that needs to be solved. During the design stage, key concepts for a solution are identified. During the implementation phase, the solution identified in the design stage is implemented in a program.

Issues discussed in the e Reuse Methodology guidelines (eRM) should be used to plan the logistics of a verification project. Issues that must be considered during this phase include:

- Software Directory Structure

- · Packaging Information and Documentation

- Naming Conventions

Use the analysis phase to gain a good understanding of the problem. In the case of functional verification, the problem is usually solved using one of the verification methodologies discussed in chapter 2. Selecting the best methodology, however, depends on the specific requirements of the verification task and can be determined by comparing the advantages and disadvantages of the different methodologies discussed in this chapter. Given any non-trivial verification task, a coverage driven verification methodology is recommended. The design phase corresponds to creating an architectural view of the selected methodology. The architectural view for a verification project is discussed in chapter 3. The implementation phase consists of building the modules in the verification environment architecture so that the desired behavior is achieved.

The following general guidelines should be used when building a verification environment in the e language:

- Break up the activities in the verification environment according to the architectural representation described in chapter 3.

- Model verification environment modules using the **unit** construct.

- Model the interface between these modules as abstract port definitions using e-Ports.

- Model abstract data types using the struct construct.

- Organize the program implementation into two dimensions: modules and aspects. Modules define the core implementation of each module. Aspects span modules and define properties or functions of these core implementations that can be changed or enhanced.

- Implement environment modules in the following order:

- Stimulus Generators

- Collectors and Monitors

- · Protocol and Data Checking

- Coverage Collection

- Follow eRM guidelines for integrating existing *e* verification components (eVCs) into the verification environment.

#### 1.4 Book Structure

This book consists of 7 parts:

- Part I: Describes functional verification methodologies and environment architecture independent of any programming language. Topics discussed will be used to motivate the features of the e language (chapters 2 and 3).

- Part II: Introduces e as a programming and verification language. The descriptions in these chapters are meant to give reader a comprehensive understanding of features of the e language (chapters 4 and 5).

- Part III: Describes the operation of the constrained random generation utility in *e*, and discusses details of creating the verification environment, stimulus generation, and verification scenario generation (chapters 6, 7, and 8).

- Part IV: Describes the details of temporal expressions and messages, and the architecture and implementation of monitors, collectors, data checkers, and protocol checkers (chapters 9, 10, 11, and 12).

- Part V: Describes the concepts of coverage collection and issues related to coverage collection and coverage analysis (chapters 13 and 14).

- Part VI: Describes the e Reuse Methodology (eRM) and covers in detail the contents of

si\_util utility package (chapters 15 and 16).

• Appendices: Describes the grammar for the *e* language in the BNF format. Also gives the list of *e* keywords, and provides checklists for following the eRM guidelines (Appendices A, B, and C).

#### 1.5 Book Conventions and Visual Cues

The visual cues in this book are shown in the following table. These conventions are used to enhance your understanding of the material. *e* keywords are shown using "times bold" typeset to prevent confusion when these terms are included in the main text flow. For example writing "the is also extension mechanism can be used" leads to ambiguities which are clarified when the appropriate keyword typeset is used as shown in the following: "the **is also** extension mechanism can also be used."

New terms are indicated with the appropriate typeset wherever a definition for these terms are given. By providing a different typeset for new terms, these terms can easily be located and their definition found.

| Visual Cue              | Description                                    |

|-------------------------|------------------------------------------------|

| Times                   | Book text                                      |

| Arial                   | <i>e</i> program text                          |

| Arial Bold              | <i>e</i> program text in book descriptive text |

| Times Bold              | <i>e</i> keywords                              |

| Times Italic Underlined | NewTerms                                       |

Sample e programs are shown either as e program fragments or as e programs. An e program refers to a code segment that can be compiled by an e compiler as shown in the text. The following is an example of an e program:

```

1 ; <'

2 ; extend sys {

3 ; d: uint;

4 ; };

5 ; '>

```

*e* Programs are indicated by the solid lines before and after the example body. Code fragments refer to sample code that cannot be loaded into an *e* compiler without adding missing parts of the program. The following shows an example of a code fragment:

#### 1.6 Summary

This chapter provided an overview on how this book is best used for learning the e language, and how to use e to solve your verification problems. While reading this book, your first focus should be on understanding the methodologies and the programming paradigms that make e the language of choice for building your verification environment. Your knowledge of syntax will grow as you gain more experience in writing verification programs and building verification environments. As you learn e, keep in mind that the full power of a programming language is unleashed only when used as intended.

# PART 1

# Verification Methodologies and Environment Architecture

#### **CHAPTER 2**

# Verification Methodologies

In recent years, significant advances in chip and system fabrication technologies have afforded designers the ability to implement digital systems with ever increasing complexity. This trend has led to a productivity gap between design methodologies and implementation technologies where because of this gap, designs produced by existing methodologies do not yield enough gates per engineer per month to meet the strict time-to-market deadlines inherent in competitive markets. The realization that functional verification now consumes anywhere between 50% to 70% of the design cycle, has brought functional verification center stage in the effort led by the design community to close this productivity gap.

The focus on functional verification has consisted of a multi-faceted approach where verification productivity improvements are made possible through introduction of:

- New verification methodologies better suited for the verification of complex systems

- Reusable verification components

- · Hardware Verification languages to facilitate the new verification paradigms

Verification methodologies and reusable components are abstract concepts that lead to verification productivity improvements, while new hardware verification languages are the enabling technology for these new concepts. This chapter presents the basics of functional verification and suggests metrics for measuring the quality of a verification methodology. It then presents the evolution of verification methodologies from task based verification to coverage driven constrained random based verification and beyond. The verification methodologies.

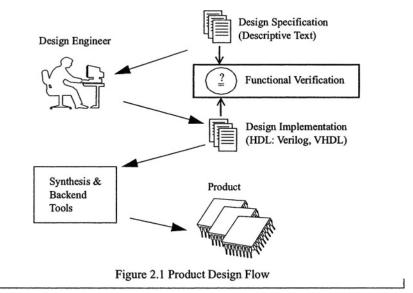

#### 2.1 Functional Verification

The typical design flow and its associated design and verification tasks are shown in figure 2.1. All design activity starts from the design specification. The task of a design team is to create a hardware implementation through their interpretation of the design specification. This initial implementation is translated into the final implementation through a series of steps where appropriate design automation tools are used to move from one level of abstraction to the next at each step. For example in an ASIC design flow starting at the RT level, the initial RTL implementation is created by the design team from the design specification. The RTL implementation is then synthesized into a netlist targeting the target implementation technology. This netlist is then processed through physical design stages to prepare the final mask information used for semiconductor fabrication.

Perhaps the most tedious and error prone step in the design flow is the manual translation of the design specification into the initial design implementation. Generally speaking, other design tasks are less prone to functional errors because of the high degree of automation involved in performing these later steps. The main reasons for functional errors in a design are:

- · Ambiguities in the design specification

- · Misunderstandings by the designer even when the specification is clear

- · Implementation errors even when the implementation goal is clear

The primary goal of *Functional Verification* is to verify that the initial design implementation is functionally equivalent to the design specification.

#### 2.1.1 Black-Box vs. White-Box Verification

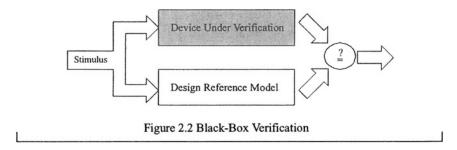

From a functional verification point of view, it is sufficient to verify a design implementation by checking its behavior on its boundary (i.e. input and output ports). If a property of a device cannot be verified through its ports, then that property is either not controllable (i.e. cannot be activated), or not observable. This verification approach is called <u>Black-Box verification</u>. The diagram in figure 2.2 shows the verification architecture for performing black-box verification. Note that in this approach, a reference model is required to check that the response generated by the device is in fact the expected response.

The features that give a design implementation its performance edge are often not visible through device ports. For example, in an instruction accurate CPU verification environment, a CPU with an instruction pipeline would functionally seem to behave the same as a CPU without an instruction pipeline. To verify the correct operation of this instruction pipeline, it is necessary to examine the design and monitor the instruction pipeline behavior and verify that it is providing the performance improvement that the CPU designers intended. In another example, consider the settings for FIFO thresholds that are used to trigger FIFO read or write operations. Correct operation of such threshold settings would be very hard to verify without visibility into the device. Even though it is possible to create a cycle accurate reference model to check for such internal behaviors through the device ports, the effort associated with building such an accurate model would make black-box verification impractical in most instances.

Even in cases where a specific feature may be verified through device ports, the difference between the time the bug is activated and the time that bug is observed would make any causality analyses difficult to track. To enhance debugability, introduce monitors that track internal properties with the potential to become sources of device malfunctions.

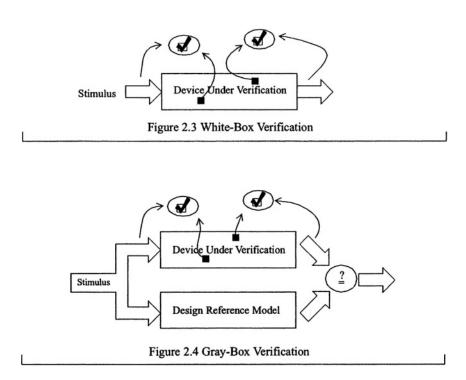

White-Box and Gray-Box verification approaches are two alternative approaches that overcome limitations of black-box verification. <u>White-Box Verification</u> (figure 2.3) refers to verifying a design through checkers (assertion checkers and monitors) without using a reference design. <u>Gray-Box Verification</u> (figure 2.3) refers to verifying a design by using a reference model but using checkers (assertions checkers and monitors) to improve verification productivity.

White-box functional verification is usually used for smaller modules in the early stages of the design process. This verification approach is hard to reuse and hard to mange. On the other hand, Black-box testing is easy to reuse as the verification project moves from module level to system level. However, the long latency for detecting bugs, the potential to miss critical internal state bugs, and the need to build a detailed reference model make Black-box verification difficult to use in practice. Gray-box testing allows the verification engineer to strike the right balance between design property checking and building a reference model. Therefore, gray-box verification is the approach that provides the most benefit throughout the verification flow.

## 2.1.2 Verification Challenges

As digital devices get more complex and time-to-market requirements become shorter, extra pressure is placed on verification engineers to complete exponentially more complex verification projects in shorter time periods. A number of challenges must be addressed in order to deal with the increasing complexity of successfully completing a functional verification project. These challenges are:

- Productivity

- Efficiency

- Reusability

- Completeness

<u>Verification Productivity</u> is defined as the ability to handle larger designs in a shorter time. For design engineers, these productivity gains have been made possible by moving from transistor level design to gate level design to RT and system level design methodologies. By designing at the RT level, design engineers can plan much larger circuits than if they were designing using discrete transistors. The same type of productivity gains must be afforded to verification engineers to allow them to deal with increasingly larger devices. Such productivity gains are achieved by moving to higher levels of abstraction both in terms of verification utilities and functional blocks that are being verified. New methodologies taking advantage of such new abstractions should be introduced so that the gap between design and verification productivity can be bridged.

<u>Verification Efficiency</u> is a measure of human intervention required to complete a verification task. With the increasing complexity of devices, it is desirable to reduce manual intervention or manual handling to as little as possible. Verification efficiency is increased by means of automation in the verification environment and through introduction of verification tool utilities, which with appropriate verification methodology, lead to a reduction of manual intervention.

<u>Verification Reusability</u> refers to the ability to reuse an existing verification environment, or pieces of an existing verification environment for new projects or later generations of the same project. Reusability is addressed by developing a modular architecture for the verification environment where modules boundaries are identified as pieces that are reuse-candidates in new projects. Additional gains can be made through better documentation of the verification architecture and the use of software programming and maintenance techniques available that simplify code enhancement

<u>Verification Completeness</u> is the goal to cover as much of the design functionality as possible. Improving verification productivity, efficiency, and reusability will provide more time to focus on improving verification completeness. It is also possible to further improve completeness by introducing verification methodologies that focus on this issue and facilities that give greater visibility to verification progress.

Clearly, addressing these challenges effectively is only possible through a comprehensive and multi-faceted approach. In short, these verification challenges must be addressed through:

- · New verification methodologies

- · Moving to higher levels of abstraction

- Using modular design techniques

- · Measuring verification progress

- · Reducing manual effort through automation

- · Improved software development environment

- · Better documentation

- Using software development techniques

- · New verification language features (utilities) to facilitate these new methodology and

software development requirements

## 2.1.3 Simulation Based Verification

The fundamental operation in simulation based verification is the process of device state activation followed by device response checking (figure 2.5). In this operation, the device is placed in a specific state and correct device response at that state is checked. Note that in this representation, a device state may refer to a simple device state as defined by the contents of its registers and status of its state machines. A state in this representation may also represent an operating mode of the device where the device may go through many simple states while operating in that mode. For example, in a state machine, the device state in this diagram may refer to a specific state of the state machine, while for a bus interface module, a state may refer to write or read operation cycles for the interface module.

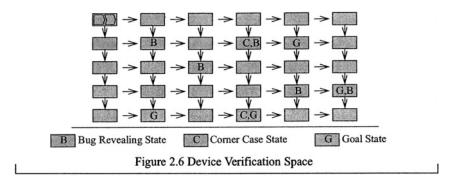

All functional verification requirements can be described as a series of such fundamental operations. Figure 2.6 shows a conceptual representation of the verification space for a given device. This representation describes the relationship between simulation steps in terms of the stimulus required to move the device into a given state.

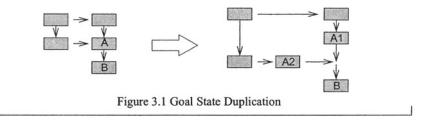

At the beginning of a verification project, the verification team establishes <u>Goal States</u> in the verification space that must be reached sometime during the simulation run. The aim of verification would be to generate the necessary stimulus to put the device into these goal states. As the device moves into new states on its way to the goal state, checkers guarantee the correct device response at each step. Because of the abstract definition of a device state where each state may also represent a device operating mode, it is possible to define a hierarchical verification space where at the higher levels, such a diagram describes correct device operation as it moves from one mode of operation to another, while at lower levels, such a diagram represents correct device operation at the most detailed level.

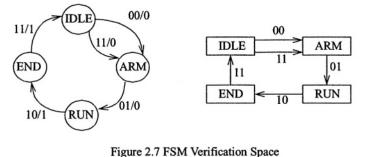

Consider a state machine and its corresponding verification space shown in figure 2.7. In this representation, each state in the verification space corresponds to a state in the original state machine. In addition, the necessary check at each step is that the current state is valid based on previous state and the input values, and that the output generated at that state is as expected.

Figure 2.7 FSWI verification Space

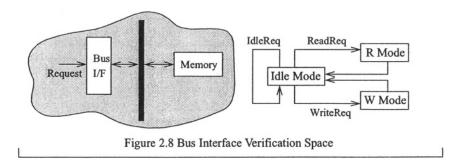

The verification space for a bus interface module, shown in figure 2.8, gives verification targets in terms of modes of operation for the bus interface module.

It should be noted that verification goals often depend not only on reaching a specific state, but also on how that verification target is reached. For example, in the finite state machine shown in figure 2.7, it is possible to reach state **ARM** through two different input combinations. Measuring verification progress therefore requires that not only target states are considered but also how these target states were reached.

## 2.1.4 Verification Terminology

The verification space as described in the previous section, is used to define the terminology for functional verification.

Each interesting scenario that should be verified is a <u>Verification Scenario</u> (VS). A verification scenario is described in terms of a sequence of verification state traversals in the verification space. A <u>Verification Item</u> is the verification step (i.e. simulation run) that verifies the correctness of one or more verification scenarios. This can happen if a simulation run traverses a path in the verification space that spans multiple verification scenarios. The collection of verification scenarios form the <u>Verification Plan</u> (VP). The <u>Verification Suite</u> is the collection of verification items that verifies all scenarios in a verification plan. The design implementation that is being verified is the <u>Device Under Verification (DUV)</u>. The <u>Verification Environment</u> (<u>VE</u>) (i.e. <u>Verification Bench</u>) is the collection of DUV and all verification related constructs.

In the context of verification environment development, <u>*Physical Level*</u> refers to signal descriptions at the bit and bit vector levels. Physical views are used to describe DUV at the hardware level. <u>*Logical View*</u> refers to any abstracted view in the design or environment. A logical view of data traffic may correspond to the data frame representation of physical level values. A logical view of a DUV may correspond to its user interface at a task level (i.e. write to device, read from device). <u>*Physical Interface*</u> refers to ports that are described at the physical level. <u>*Logical Interface*</u> refers to port interfaces that are described at a logical level.

## 2.2 Verification Metrics and Verification Quality

Verification methodologies are adopted according to their benefit. It is therefore necessary to identify a number of metrics that will be used to measure the effectiveness of a verification methodology. This section presents a number of verification methodologies. The metrics presented in this section are closely related to the verification challenges discussed in section 2.1.2. Some of these metrics are measured quantitatively while others are used as qualitative guidelines for discussing merits of verification methodologies.

The following metrics are considered in measuring the value of a verification methodology:

- Granularity

- Productivity

- Effectiveness

- Completeness

- · Reusability of the Verification Environment

- Reusability of the Simulation Data

Verification Quality refers to the combination of these verification metrics.

## 2.2.1 Granularity

<u>Verification Granularity</u> is a qualitative metric used to measure the degree of detail (i.e. granularity) that should be considered in crafting a verification plan, and subsequently completing the verification project. The ultimate goal is to allow verification engineers to deal with verification concepts at the highest level of abstraction possible. It is important to note that in functional verification, it is ultimately the traffic at the physical level (logic values on device signals) that should be verified. In this context, moving to a higher level of abstraction is only possible if the handling of the layer hidden under this newly introduced abstraction can be automated without loss of any detail at the physical level.

The move to a higher level of abstraction comes in two forms:

- Verification Goal Abstraction:

- Deal with less detailed tasks

- Higher Level Verification Language Constructs

- Write less code for same task

- · Make fewer mistakes in developing the environment

Verification goal abstraction allows the verification engineer to concentrate on higher level data constructs instead of logic values on device wires. For example, by providing an ethernet verification component, a verification engineer can define a verification goal as "injecting a valid ethernet packet" instead of having to describe the sequence of activity that will lead to such a packet at the device port. In this case, the ethernet verification component handles all the detail necessary to inject a valid packet. It is therefore important to pay careful attention to the design and usage of verification components used to architect a verification environment.

More powerful Language constructs allow the verification engineer to implement the same task in fewer lines of code and therefore a shorter time. As is commonly known in software development, the number of bugs in a software program is proportional to the number of lines of code. Thus, by reducing the verification code size, the potential for errors in verification code is also reduced.

## 2.2.2 Productivity

<u>Verification Productivity</u> is a measure of the amount of manual effort that is involved in a verification project. This manual effort consist of:

- Developing the verification environment

- · Verifying all verification scenarios in the verification plan

- Maintaining the verification environment

- · Migrating the verification environment for next project

Maintaining and migrating a verification environment includes measures that should be anticipated during the development of the verification environment. The main focus in developing a methodology for improving productivity is to minimize the amount of manual effort required to develop the environment and create the set of items that verify all scenarios in the verification plan.

As in most engineering tasks, there is a fine balance between the effort spent on environment development and the effort required to create the set of all necessary verification items (verification suite). The more time is spent on development, the less time spent on creating the verification suite, and vice vera. For example, if the verification environment is complex enough to handle all corner cases automatically, then the manual effort required to test corner cases is very small. In general, considering all possible corner cases in a verification environment can be very time consuming and it is often best to verify such extreme corner cases through manually created verification items. The remainder of this chapter provides methodology guidelines that help in striking the right balance between these two efforts.

## 2.2.3 Effectiveness

During simulations runs, the goal is to verify all the scenarios described in the verification plan. <u>Verification Effectiveness</u> provides a measure for the contribution of a simulation run to the overall task of verifying all the scenarios in the verification plan. Ideally, all time spent in running any simulation should improve verification plan coverage.

## 2.2.4 Completeness

<u>Verification Completeness</u> is a measure of the portion of device function verified during the course of the verification project. Generally, no verification plan can completely specify all features and all possible corner cases. Although it is relatively easy to define a measure of completeness for a verification plan (i.e. measure how many scenarios have been covered), it is difficult to measure completeness when referring to all possible features of a design.

Since completing all verification scenarios in a verification plan is a required goal for the verification project, then verification completeness is concerned with the part of device function that may not be specified explicitly in a verification plan but is indirectly verified during the verification project.

In a verification environment where each scenario is explicitly verified (i.e. directed verification), completeness of device verification is hardly extended beyond the verification plan scenarios. However, in a verification methodology where verification scenarios are randomly generated and device response is automatically checked, it is highly likely that many scenarios beyond the initial verification plan are also verified.

#### 2.2.5 Verification Environment Reusability

Verification Environment Reusability may be defined in two ways:

· Reusing verification environment for next generations of the same design

• Reusing verification environment modules and utilities while moving from module level verification to system level verification

The main assumption in re-using a verification environment across design generations is that design generations have similar profiles and features, though slightly modified or enhanced. The main challenge in achieving this target is to anticipate future design changes and to identify modules and features that are expected to change. By defining clear architectural boundaries between pieces that are expected to change and the pieces that are expected to remain the same, the environment migration tasks can be drastically reduced.

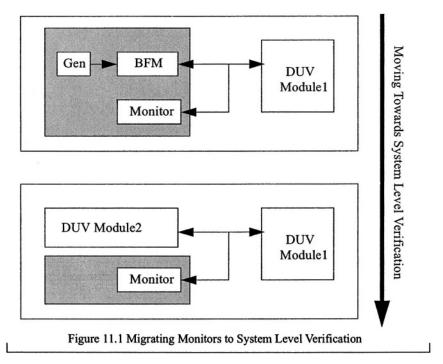

Reusing the verification environment through the project life-cycle is a more pressing requirement for projects where turnaround time is very important. As verification tasks move from module level verification to system level verification, verification is less focused on generation and more attention is placed on collection, monitoring, and coverage collection. A general guideline for achieving this target is to architect the verification environment such that the required pieces for system level verification (monitors, checkers, coverage collectors) can function independently from the generators.

## 2.2.6 Simulation Result Reusability

<u>Simulation Results</u> refers to the data that is collected during simulation runtime. It is often the case that after a long simulation run is completed, either the need to check some additional properties is realized, or it would be useful to find out if a certain scenario was in fact exercised during the simulation run. At one extreme, if a signal change dump of all signals during the simulation run is available, all such questions can be answered by analyzing the simulation data dump. At another extreme, if no data is stored, then the entire simulation has to be rerun for any question to be answered. The right approach is obviously to strike a good balance between the amount of collected data and the types of questions that may need to be answered after a simulation run is completed. <u>Simulation Result Reusability</u> refers to the ability to selectively define the information collected during simulation run so that post-simulation analysis can be performed without having to re-run the simulation.

Consider a multiplier design that multiplies two 16 bit numbers. If we collect a list of all pairs of numbers that have been multiplied during simulation, we can answer any question on whether the multiplier has been tested for a given pair of numbers without having to rerun the simulation. Not only is it is important to collect the numbers seen on each input port, but the correlation between these input values should also be recorded.

Data reusability is usually considered as part of coverage collection strategy. During coverage collection, it is very important to collect information on specific coverage questions, and also to anticipate future questions that may arise and if possible, collect the necessary data to answer such questions without having to rerun the simulation.

## 2.3 Directed Test Based Verification

<u>Directed Test based verification</u> is a brute force technique for completing a verification project. In this approach, a specific verification item is created for each verification scenario and new facilities are implemented, or the existing infrastructure is enhanced to support the requirements for each new verification scenario.

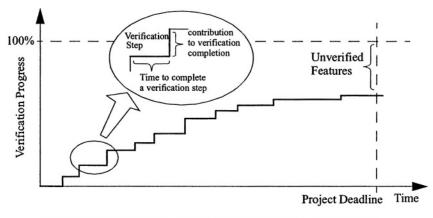

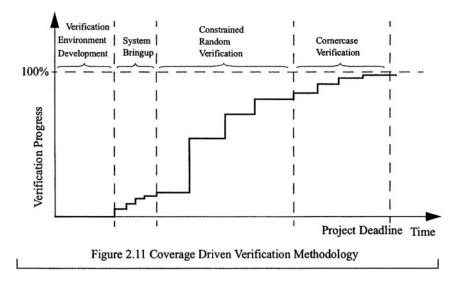

The one and only potential advantage of a directed test based verification methodology is that project progress is almost linearly proportional to the amount of time spent on the project (figure 2.9). In this approach, verification progress is made one time-consuming and small step at a time. A directed test based verification methodology may be recommended for a verification environment that lacks modern verification tools and languages, or for projects where very little time is available to complete the verification phase and therefore insufficient time is devoted to target full verification. Studying directed test based verification is useful for two reasons: first, the need for more advanced verification methodologies is motivated by studying the shortcomings of this approach. Second, a directed test based approach may be used as part of other verification methodologies to cover very hard to reach corner case verification requirements.

Figure 2.9 Verification Progress and Directed Test Based Verification

The fundamental steps in directed test based verification are very simplistic. These steps are:

- Complete the verification plan

- Sort the scenarios in the verification plan according to some priority considerations

- For each scenario, enhance the existing environment, or build new infrastructure to verify that specific scenario

- · Add the completed verification item to the verification suite for regression

The sorting of verification scenarios in this approach may depend on multiple factors, including the importance of the features that are verified, the natural order of verification code development as the verification environment is being enhanced, and the order of development for the device under verification.

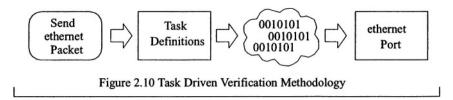

## 2.3.1 Task Driven Verification Methodology

Directed test based verification in its most fundamental form interacts with the DUV using physical level signals. This low level interaction and modeling introduces major inefficiencies in building the verification environment and verifying scenarios. <u>Task Driven Verification</u> <u>Methodology</u> is a variant of the directed test based verification methodology where logical views are used to improve verification productivity (figure 2.10). In task driven verification methodology:

- Traffic is defined at a higher level of abstraction (frames, packets, instructions etc.).

- Verification tasks are defined at a logical level (write to port, read from port, issue instruction, etc.)

- Verification utilities are developed to support these new data structure and task definitions

- Verification scenarios are created one scenario at a time using the available verification utilities

## 2.3.2 Verification Quality

The brute nature of directed test based verification leads to significant loss of productivity. In such cases, the most fundamental shortcoming is that each verification scenario has to be considered independently and human interaction is required to set up the verification environment, generating the necessary traffic, and checking results for each verification scenario. At the same time, the verification plan may describe scenarios using ranges of acceptable values for each parameter. Using a directed test based approach, the values for these parameters have to be specifically decided, and often, additional scenarios created for corner cases consist of specific combinations of such parameters. The main problem with this approach is that it is difficult and time consuming to enumerate values for different parameters and come up with corner case conditions.

Additionally, because of the amount of hard-coded values in a directed test based approach, such a verification environment is hard to maintain and not easily portable even across very similar projects.

To summarize, the advantages of task driven verification methodology are:

- Improves productivity over the most basic task driven verification methodology by introducing tasks and abstract data types

- Useful as part of a more comprehensive verification methodology to cover very specific corner cases

The disadvantages, however, include:

- Requiring human interaction to create and check each scenario, leading to very low productivity

- Requiring detailed enumeration of all scenarios and corner cases (often too numerous to be possible) leading to verification incompleteness

- Difficult to use, tedious to maintain, and impossible to port across projects because of extreme customization of each verification item

Random generation of data and scenarios is used to improve on the shortcomings of task driven verification methodology. This verification methodology in described in the next section.

## 2.4 Constrained Random Test Based Verification

Randomization is a powerful technique, which, when used appropriately, can drastically improve verification quality. A closer look at the anatomy of a verification scenario can lead to a better understanding of the way randomization is leveraged to improve verification quality.

A verification scenario describes a well defined order of low level transactions in the verification environment where a set of data and parameter values are associated with each low level transaction<sup>1</sup>. Ideally, a set of atomic transactions can be defined where any verification scenario is composed of a sequence of these atomic transactions. Each atomic transaction will require a set of data and parameter objects to complete its activity. Obviously, not all sequences of such atomic transactions lead to meaningful scenarios. At the same time, not all possible data and parameter combinations are allowed for a given atomic transaction. The legality of valid data and parameters may depend on the context (i.e. order of an atomic transaction within a sequence).

<sup>&</sup>lt;sup>1</sup> A parameter modifies the behavior of a transaction while data does not. For example, for a bus read transaction, read burst size is a transaction parameter since it modifies the number of bus cycles, etc., while address to read from is considered transaction data since the transaction behavior is generally independent of its value.

Assume a list of such atomic transactions and their corresponding valid orderings, valid data content, and valid parameter content is available for a DUV. It is then straight forward to see that given enough time, all verification scenarios in the verification plan can be created by generating random sequences of these atomic transactions along with their corresponding data and parameters, while constraining the random generation to the subset of valid sequences, data values, and parameter settings.

<u>Constrained Random Test Based</u> leverages the concept of randomization to automatically generate constrained random sequences that by exercising the necessary device functions, verify the scenarios in the verification plan. This methodology leads to immediate and significant gains in verification productivity and completeness.