# The Circuits and Filters Handbook Third Edition

# Computer Aided Design and Design Automation

Edited by

Wai-Kai Chen

# Computer Aided Design and Design Automation

# The Circuits and Filters Handbook

# **Third Edition**

Edited by

Wai-Kai Chen

Fundamentals of Circuits and Filters

Feedback, Nonlinear, and Distributed Circuits

Analog and VLSI Circuits

Computer Aided Design and Design Automation

Passive, Active, and Digital Filters

# The Circuits and Filters Handbook Third Edition

# Computer Aided Design and Design Automation

Edited by

Wai-Kai Chen

University of Illinois

Chicago, U.S.A.

CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742

© 2009 by Taylor & Francis Group, LLC CRC Press is an imprint of Taylor & Francis Group, an Informa business

No claim to original U.S. Government works Printed in the United States of America on acid-free paper 10 9 8 7 6 5 4 3 2 1

International Standard Book Number-13: 978-1-4200-5918-2 (Hardcover)

This book contains information obtained from authentic and highly regarded sources. Reasonable efforts have been made to publish reliable data and information, but the author and publisher cannot assume responsibility for the validity of all materials or the consequences of their use. The authors and publishers have attempted to trace the copyright holders of all material reproduced in this publication and apologize to copyright holders if permission to publish in this form has not been obtained. If any copyright material has not been acknowledged please write and let us know so we may rectify in any future reprint.

Except as permitted under U.S. Copyright Law, no part of this book may be reprinted, reproduced, transmitted, or utilized in any form by any electronic, mechanical, or other means, now known or hereafter invented, including photocopying, microfilming, and recording, or in any information storage or retrieval system, without written permission from the publishers.

For permission to photocopy or use material electronically from this work, please access www.copyright.com (http://www.copyright.com/) or contact the Copyright Clearance Center, Inc. (CCC), 222 Rosewood Drive, Danvers, MA 01923, 978-750-8400. CCC is a not-for-profit organization that provides licenses and registration for a variety of users. For organizations that have been granted a photocopy license by the CCC, a separate system of payment has been arranged.

**Trademark Notice:** Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation without intent to infringe.

### Library of Congress Cataloging-in-Publication Data

Computer aided design and design automation / Wai-Kai Chen.

p. cm.

Includes bibliographical references and index.

ISBN-13: 978-1-4200-5918-2

ISBN-10: 1-4200-5918-1

$1.\ Engineering\ design.\ 2.\ Electric\ engineering--Computer-aided\ design.\ I.\ Chen,\ Wai-Kai,\ 1936-\ II.$  Title.

TA174.C58135 2009

621.3--dc22

2008048129

Visit the Taylor & Francis Web site at http://www.taylorandfrancis.com

and the CRC Press Web site at http://www.crcpress.com

# Contents

| Prefa | acevii                                                     |

|-------|------------------------------------------------------------|

| Edite | or-in-Chiefix                                              |

| Con   | tributorsxi                                                |

| SEC   | CTION I Computer Aided Design and Optimization             |

| 1     | Modeling of Circuit Performances                           |

| 2     | Symbolic Analysis Methods                                  |

| 3     | Numerical Analysis Methods                                 |

| 4     | Design by Optimization                                     |

| 5     | Statistical Design Optimization                            |

| 6     | Physical Design Automation                                 |

| 7     | Design Automation Technology                               |

| 8     | Computer-Aided Analysis                                    |

| 9     | Analog Circuit Simulation                                  |

| SEC   | CTION II Design Automation                                 |

| 10    | Internet-Based Microelectronic Design Automation Framework |

vi

| 11   | System-Level Design                                       | l <b>1</b> -1 |

|------|-----------------------------------------------------------|---------------|

| 12   | Performance Modeling and Analysis Using VHDL and SystemC  | <b>2</b> -1   |

| 13   | Embedded Computing Systems and Hardware/Software Codesign | l <b>3</b> -1 |

| 14   | Design Automation Technology Roadmap                      | l <b>4</b> -1 |

| Inde | ex                                                        | N-1           |

## **Preface**

As system complexity continues to increase, the microelectronic industry must possess the ability to adapt quickly to the market changes and new technology through automation and simulations. The purpose of this book is to provide in a single volume a comprehensive reference work covering the broad spectrum of computer aided design and optimization techniques, which include circuit performance modeling, design by optimization, statistical design optimization, physical design automation, computer aided analysis and circuit simulations; and design automation, which includes system-level design, performance modeling and analysis, and hardware/software codesign. This book is written and developed for the practicing electrical engineers and computer scientists in industry, government, and academia. The goal is to provide the most up-to-date information in the field.

Over the years, the fundamentals of the field have evolved to include a wide range of topics and a broad range of practice. To encompass such a wide range of knowledge, this book focuses on the key concepts, models, and equations that enable the design engineer to analyze, design, and predict the behavior of large-scale systems. While design formulas and tables are listed, emphasis is placed on the key concepts and theories underlying the processes.

This book stresses fundamental theories behind professional applications and uses several examples to reinforce this point. Extensive development of theory and details of proofs have been omitted. The reader is assumed to have a certain degree of sophistication and experience. However, brief reviews of theories, principles, and mathematics of some subject areas are given. These reviews have been done concisely with perception.

The compilation of this book would not have been possible without the dedication and efforts of Professor Steve Sung-Mo Kang, and most of all the contributing authors. I wish to thank them all.

Wai-Kai Chen

# Editor-in-Chief

Wai-Kai Chen is a professor and head emeritus of the Department of Electrical Engineering and Computer Science at the University of Illinois at Chicago. He received his BS and MS in electrical engineering at Ohio University, where he was later recognized as a distinguished professor. He earned his PhD in electrical engineering at the University of Illinois at Urbana–Champaign.

Professor Chen has extensive experience in education and industry and is very active professionally in the fields of circuits and systems. He has served as a visiting professor at Purdue University, the University of Hawaii at Manoa, and Chuo University in Tokyo, Japan. He was the editor-in-chief of the *IEEE Transactions on Circuits and Systems, Series I and II*, the president of the IEEE Circuits and Systems Society, and is the founding editor and the editor-in-chief of the *Journal of Circuits, Systems and Computers*. He received the Lester R. Ford Award from the Mathematical

Association of America; the Alexander von Humboldt Award from Germany; the JSPS Fellowship Award from the Japan Society for the Promotion of Science; the National Taipei University of Science and Technology Distinguished Alumnus Award; the Ohio University Alumni Medal of Merit for Distinguished Achievement in Engineering Education; the Senior University Scholar Award and the 2000 Faculty Research Award from the University of Illinois at Chicago; and the Distinguished Alumnus Award from the University of Illinois at Urbana–Champaign. He is the recipient of the Golden Jubilee Medal, the Education Award, and the Meritorious Service Award from the IEEE Circuits and Systems Society, and the Third Millennium Medal from the IEEE. He has also received more than a dozen honorary professorship awards from major institutions in Taiwan and China.

A fellow of the Institute of Electrical and Electronics Engineers (IEEE) and the American Association for the Advancement of Science (AAAS), Professor Chen is widely known in the profession for the following works: Applied Graph Theory (North-Holland), Theory and Design of Broadband Matching Networks (Pergamon Press), Active Network and Feedback Amplifier Theory (McGraw-Hill), Linear Networks and Systems (Brooks/Cole), Passive and Active Filters: Theory and Implements (John Wiley), Theory of Nets: Flows in Networks (Wiley-Interscience), The Electrical Engineering Handbook (Academic Press), and The VLSI Handbook (CRC Press).

# Contributors

### Jonathan A. Andrews

Department of Electrical and Computer Engineering Virginia Commonwealth University Richmond, Virginia

### James H. Aylor

Department of Electrical Engineering University of Virginia Charlottesville, Virginia

### Peter Bendix

Technology Modeling Associates, Inc. Palo Alto, California

### Wai-Kai Chen

Department of Electrical and Computer Engineering University of Illinois at Chicago Chicago, Illinois

### Moon-Jung Chung

Department of Computer Science Michigan State University East Lansing, Michigan

### Donald R. Cottrell

Silicon Integration Initiative, Inc. Austin, Texas

### Allen M. Dewey

Department of Electrical and Computer Engineering Duke University Durham, North Carolina

### Abhijit Dharchoudhury

Beckman Institute

University of Illinois

at Urbana–Champaign

Urbana, Illinois

### Marwan M. Hassoun

Department of Electrical and Computer Engineering Iowa State University Ames, Iowa

### Sung-Mo Kang

Office of Chancellor University of California, Merced Merced, California

### Heechul Kim

Department of Computer Science and Engineering Hankuk University of Foreign Studies Yongin, Korea

### Robert H. Klenke

Department of Electrical and Computer Engineering Virginia Commonwealth University Richmond, Virginia

### Alice C. Parker

Ming Hsieh Department of Electrical Engineering University of Southern California Los Angeles, California

### Benedykt S. Rodanski

Faculty of Engineering University of Technology Sydney, New South Wales, Australia

### J. Gregory Rollins

Technology Modeling Associates, Inc. Palo Alto, California

### Sachin S. Sapatnekar

Department of Electrical and Computer Engineering University of Minnesota Minneapolis, Minnesota

### Naveed A. Sherwani

Intel Corporation Hillsboro, Oregon

### Maciej A. Styblinski

Department of Electrical Engineering Texas A&M University College Station, Texas xii Contributors

### Yosef Tirat-Gefen

Ming Hsieh Department of Electrical Engineering University of Southern California Los Angeles, California

### Suhrid A. Wadekar

Ming Hsieh Department of Electrical Engineering University of Southern California Los Angeles, California

### Wayne Wolf

Department of Electrical Engineering Princeton University Princeton, New Jersey

### Andrew T. Yang

Apache Design Solutions, Inc. San Jose, California

I

# Computer Aided Design and Optimization

## Sung-Mo Kang

University of California, Merced

| Modeling of Circuit Performances Sung-Mo Kang and Abhijit Dharchoudhury                                                 | <b>1</b> -1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbolic Analysis Methods Benedykt S. Rodanski and Marwan M. Hassoun                                                    | <b>2</b> -1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

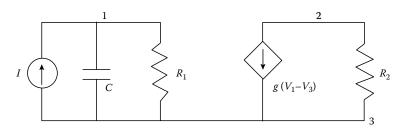

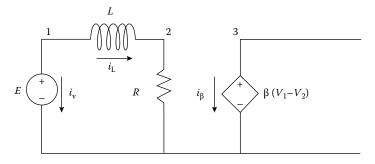

| Numerical Analysis Methods Andrew T. Yang<br>Equation Formulation • Solution of Linear Algebraic Equations • References | 3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Design by Optimization Sachin S. Sapatnekar                                                                             | <b>4</b> -1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Statistical Design Optimization Maciej A. Styblinski                                                                    | 5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Physical Design Automation Naveed A. Sherwani                                                                           | <b>6</b> -1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

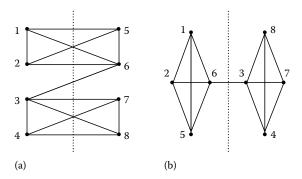

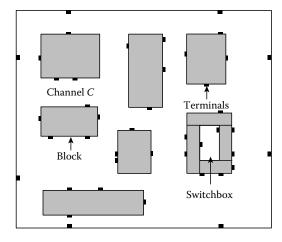

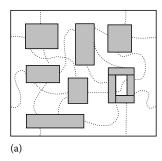

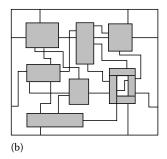

|                                                                                                                         | Introduction • Circuit Performance Measures • Input-Output Relationships • Dependency of Circuit Performances on Circuit Parameters • Design of Experiments • Least-Squares Fitting • Variable Screening • Stochastic Performance Models • Other Performance Modeling Approaches • Example of Performance Modeling • References  Symbolic Analysis Methods Benedykt S. Rodanski and Marwan M. Hassoun Introduction • Symbolic Modified Nodal Analysis • Solution Methods • Ideal Operational Amplifiers • Applications of Symbolic Analysis • Symbolic Analysis Software Packages • References  Numerical Analysis Methods Andrew T. Yang Equation Formulation • Solution of Linear Algebraic Equations • References  Design by Optimization Sachin S. Sapatnekar Introduction • Optimization Algorithms • Transistor Sizing Problem for CMOS Digital Circuits • Analog Design Centering Problem • References  Statistical Design Optimization Maciej A. Styblinski Introduction • Problems and Methodologies of Statistical Circuit Design • Underlying Concepts and Techniques • Statistical Methods of Yield Optimization • Conclusion • References  Physical Design Automation Naveed A. Sherwani Introduction • Very Large-Scale Integration Design Cycle • Physical Design Cycle • Design Styles • Partitioning • Other Partitioning Algorithms • Placement • Routing • Classification of Global Routing Algorithms • Classification of Detailed Routing Algorithms • |

| 7 | Design Automation Technology Allen M. Dewey                 | <b>7</b> -1 |

|---|-------------------------------------------------------------|-------------|

| 8 | Computer-Aided Analysis J. Gregory Rollins and Peter Bendix | <b>8</b> -1 |

| 9 | Analog Circuit Simulation J. Gregory Rollins                | <b>9</b> -1 |

1

# Modeling of Circuit Performances

| 1.1   | Introduction                                                                           | 1-1          |

|-------|----------------------------------------------------------------------------------------|--------------|

| 1.2   | Circuit Performance Measures                                                           | 1-2          |

| 1.3   | Input-Output Relationships<br>Memoryless (Static) Relationship • Dynamic Relationships | 1-3          |

| 1.4   | Dependency of Circuit Performances on Circuit Parameters                               | 1-3          |

| 1.5   | Design of Experiments                                                                  | 1-5          |

| 1.6   | Least-Squares Fitting                                                                  | <b>1</b> -11 |

| 1.7   | Variable Screening                                                                     |              |

| 1.8   | Stochastic Performance Models                                                          |              |

| 1.9   | Other Performance Modeling Approaches                                                  | 1-14         |

| 1.10  | Example of Performance Modeling                                                        |              |

| Dofor | 1000000                                                                                | 1 14         |

Sung-Mo Kang University of California, Merced

Abhijit Dharchoudhury University of Illinois at Urbana-Champaign

### 1.1 Introduction

The domain of computer-aided design and optimization for circuits and filters alone is very broad, especially since the design objectives are usually multiple. In general, the circuit design can be classified into

- · Electrical design

- · Physical design

Physical design deals with concrete geometrical parameters while electrical design deals with the electrical performances of the physical object. Strictly speaking, both design aspects are inseparable since any physical design is a realization of a particular electrical design. On the other hand, electrical design without proper abstraction of the corresponding physical design can be futile in the sense that its implementation may not meet the design goals. Thus, electrical and physical design should go hand in hand. Most literature deals with both designs using weighted abstractions. For example, in the design of a digital or analog filter, various effects of physical layout are first captured in the parasitic models for interconnects and in the electrical performance models for transistors. Then, electrical design is performed using such models to predict electrical performances. In physical design optimization, geometrical parameters are chosen such that the predicted electrical performances can meet the design

objectives. For example, in the timing-driven physical layout of integrated circuits, circuit components will be laid out, placed and interconnected to meet timing requirements. In order to make the optimization process computationally efficient, performance models are used during the optimization process instead of simulation tools. In this chapter, the focus of design optimization is on the electrical performance. The computer-aided electrical design can be further classified into performance analysis and optimization. Thus, this chapter first discusses the modeling of electrical performances, symbolic and numerical analysis techniques, followed by optimization techniques for circuit timing, and yield enhancement with transistor sizing and statistical design techniques.

### 1.2 Circuit Performance Measures

The performance of a particular circuit can be measured in many ways according to application and design goals. In essence, each performance measure is an indication of the circuit output which the designer is interested in for a particular operating condition. The circuit performance, in general, is dependent on the values of the designable parameters such as the transistor sizes, over which the designer has some degree of control, and the values of the noise parameters such as the fluctuation in power supply voltage or the threshold voltages of the transistors, which are random in nature. Also, the performance measure used is dependent on the type of the circuit. The performance measures of digital circuits are usually quite different from those of analog circuits or filters. Some of the important performance measures of digital circuits are

- · Signal propagation delay from an input to an output

- Rise and fall times of signals

- · Clock signal skew in the circuit

- · Power dissipation

- · Manufacturing yield

- Failure rate (reliability)

Important performance measures for analog circuits are

- Small-signal gain and bandwidth in frequency domain

- · Sensitivities to various nonideal factors (noise)

- Slew rate of operational amplifiers

- · Power dissipation

- · Manufacturing yield

- Failure rate (reliability)

The modeling of digital circuit performances is usually more difficult to derive than the modeling of analog circuit performances, mainly due to the nonlinear nature of digital circuits. Thus, simple transistor models have been used often to obtain simple qualitative models for propagation delays, rise and fall times, and power dissipation. On the other hand, due to the small-signal nature, the device models required by analog designers need to be much more accurate. Another important performance measure is the manufacturing yield, which determines the product cost. The yield depends on both the quality of manufacturing process control and the quality of the design. A challenging design problem is how to come up with a design which can be robust to nonideal manufacturing conditions and thereby produce a good manufacturing yield. The model for failure rate is difficult to derive due to several complex mechanisms that determine the lifetime of chips. In such cases, empirical models, which are not physical, have been introduced.

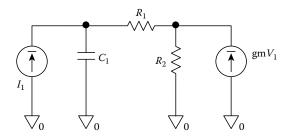

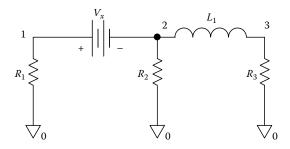

In order to develop models for analog circuits, transistors in the circuit are first DC-biased at the proper biasing points. Then, small-signal circuit models are developed at those DC operating points. The resulting linear circuits can be analyzed by either using mathematical symbols (symbolic analysis) or by using simulators.

### 1.3 Input-Output Relationships

The circuit functionally depends on the input-output relationships and thus circuit specifications and test specifications are made on the basis of the input-output relationships. For modeling purposes, the input-output relationships can be classified into static relationships and dynamic relationships.

### 1.3.1 Memoryless (Static) Relationship

A given input–output pair is said to have a memoryless relationship if it can be described statically without the use of any ordinary or partial differential equation. It is important to note that the choice of input and output variables can determine the nature of the relationship. For instance, the relationship between input charge q and the output voltage v in a 1 F capacitor is static. On the other hand, the relationship between an input current i and the output voltage v, in the same capacitor is nonstatic since the voltage is dependent on the integral of the input current. Ideally, basic circuit elements such as resistor, capacitor, inductor, and source should be characterized by using static relationships, so-called constitutive relationships, with proper choice of input and output variables. However, for circuits and systems design, since their input–output relationships are specified in terms of specific variables of interest, such choice of variables cannot be made arbitrarily. Often, both input and output variables are voltages, especially in digital circuits.

### 1.3.2 Dynamic Relationships

A given input–output pair is said to have a dynamic relationship if the modeling of the relationship requires a differential equation. In most cases, since the circuits contain parasitic capacitors or inductors or both, the input–output relationship is dynamic. For instance, the input–output relationship of an inverter gate with capacitive load  $C_{load}$  can be described as

$$C_{\text{load}} \frac{\text{d}V_{\text{out}}}{\text{d}t} = i(V_{\text{out}}, V_{\text{in}}, V_{\text{DD}})$$

(1.1)

where

$V_{

m out}$  and  $V_{

m in}$  denote the output and input voltages i denotes the current through the pull-up or pull-down transistor  $V_{

m DD}$  denotes the power supply voltage

Although the relationship is implicit in this case, Equation 1.1 can be solved either analytically or numerically to find the relationship. Equation 1.1 can be generalized by including noise effects due to variations in the circuit fabrication process.

### 1.4 Dependency of Circuit Performances on Circuit Parameters

Circuit performances are functions of circuit parameters, which are usually not known explicitly. In order to design and analyze analog or digital circuits, the dependency of the circuit performances on the various circuit parameters need to be modeled.

The actual value of a circuit parameter in a manufactured circuit is expected to be different from the nominal or target value due to inevitable random variations in the manufacturing processes and in the environmental conditions in which the circuit is operated. For example, the actual channel width W of an MOS transistor can be decomposed into a nominal component  $W^0$  and a statistically varying component  $\Delta W$ , i.e.,  $W = W^0 + \Delta W$ . The nominal component is under the control of the designer and can be set to a particular value. Such a nominal component is said to be designable or controllable, e.g.,  $W^0$ .

The statistically varying component, on the other hand, is not under the control of the designer and is random in nature. It is called the noise component, and it represents the uncontrollable fluctuation of a circuit parameter about its designable component, e.g.,  $\Delta W$ . For certain circuit parameters, e.g., device model parameters (like the threshold voltages of MOS transistors) and operating conditions (like temperature or power supply voltage), the nominal values are not really under the control of the circuit designer and are set by the processing and operating conditions. For these circuit parameters, the nominal and random components are together called the noise component. In general, therefore, a circuit parameter  $x_i$  can be expressed as follows:

$$x_i = d_i + s_i \tag{1.2}$$

where

$d_i$  is the designable component  $s_i$  is the noise component

It is common to group all the designable components to form the set of designable parameters, denoted by  $\mathbf{d}$ . Similarly, all the noise parameters are grouped together to form the noise parameters, denoted by the random vector  $\mathbf{s}$ . Vectorially, Equation 1.2 can be rewritten as

$$\mathbf{x} = \mathbf{d} + \mathbf{s} \tag{1.3}$$

A circuit performance measure is a function of the circuit parameters. For example, the propagation delay of a CMOS inverter circuit is a function of the nominal channel lengths and widths of the NMOS and PMOS transistors. It is also a function of the threshold voltages of the transistors and the power supply voltage. Thus, in general, a circuit performance is a function of the designable as well as the noise parameters:

$$y = y(\mathbf{x}) = y(\mathbf{d}, \mathbf{s}) \tag{1.4}$$

If this function is known explicitly in terms of the designable and noise parameters, then optimization methods can be applied directly to obtain a design which is optimal in terms of the performances or the manufacturing yield. More often than not, however, the circuit performances cannot be expressed explicitly in terms of the circuit parameters. In such cases, the value of a circuit performance for given values of circuit parameters can be obtained by circuit simulation. Circuit simulations are computationally expensive, especially if the circuit is large and transient simulations are required. A compact performance model in terms of the circuit parameters is an efficient alternative to the circuit simulator. Two factors determine the utility of the performance model. First, the model should be computationally efficient to construct and evaluate so that substantial computational savings can be achieved. Second, the model should be accurate.

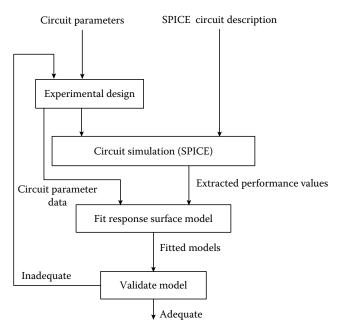

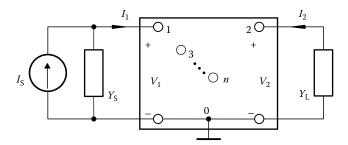

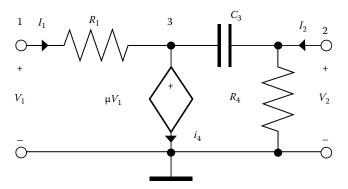

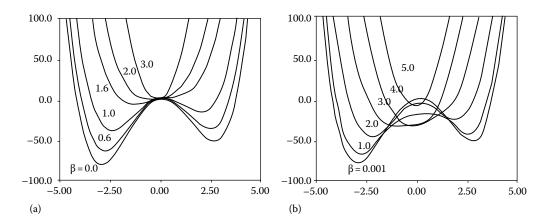

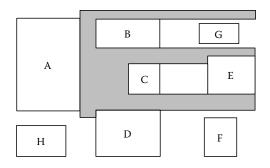

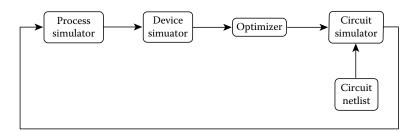

Figure 1.1 shows the general procedure for constructing the model for a performance measure y in terms of the circuit parameters  $\mathbf{x}$ . The model-building procedure consists of four steps. In the first stem, m training points are selected from the  $\mathbf{x}$ -space. The ith training point is denoted by  $\mathbf{x}_i$ ,  $i=1,2,\ldots,m$ . In the second step, the circuit is simulated at these m training points and the values of the performance measure are obtained from the circuit simulation results as  $y(\mathbf{x}_1), y(\mathbf{x}_2), \ldots, y(\mathbf{x}_m)$ . In the third step, a preassigned function of y in terms of  $\mathbf{x}$  is "fitted" to the data. In the fourth and final step, the model is validated for accuracy. If the model accuracy is deemed inadequate, the modeling procedure is repeated with a larger number of training points or with different models.

The model is called the response surface model (RSM) [1] of the performance and is denoted by  $\hat{y}(\mathbf{x})$ . The computational cost of modeling depends on the number of training points m, and the procedure of fitting the model to the data. The accuracy of the RSM is quantified by computing error measures which

FIGURE 1.1 Performance modeling procedure.

quantify the "goodness of fit." The accuracy of the RSM is greatly influenced by the manner in which the training points are selected from the x-space. Design of experiment (DOE) [2] techniques are a systematic means of obtaining the training points such that the maximum amount of information about the model can be obtained from these simulations or experimental runs. In the next section, we review some of the most commonly used experimental design techniques in the context of performance optimization and statistical design. To illustrate certain points in the discussion below, we will assume that the RSM of the performance measure y is the following quadratic polynomial in terms of the circuit parameters:

$$\hat{y}(\mathbf{x}) = \hat{\alpha}_0 + \sum_{i=1}^n \hat{\alpha}_i x_i + \sum_{i=1}^n \sum_{j=1}^n \hat{\alpha}_{ij} x_i x_j$$

(1.5)

where the  $\hat{\alpha}s$  are the coefficients of the model. Note, however, that the discussion is valid for all RSMs in general.

### 1.5 Design of Experiments

### 1.5.1 Factorial Design

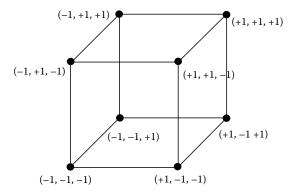

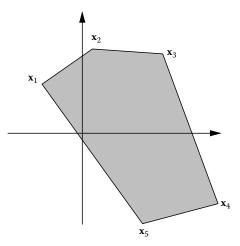

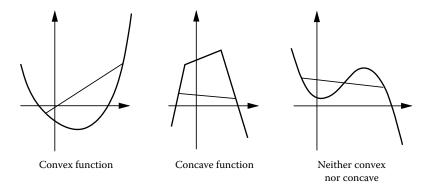

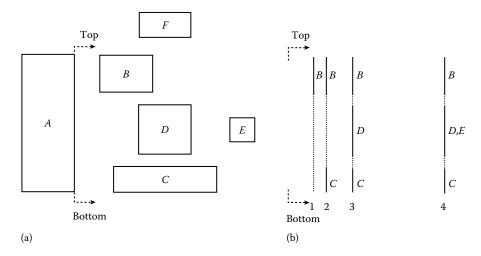

In this experimental design, each of the circuit parameters  $x_1, x_2, ..., x_n$  is quantized into two levels or settings, which are denoted by -1 and +1. A full factorial design contains all possible combinations of levels for the n parameters, i.e., it contains  $2^n$  training points or experimental runs. The design matrix for the case of n = 3 is shown in Table 1.1 and the design is pictorially described in Figure 1.2. The value of the circuit performance measure for the kth run is denoted by  $y_k$ .

Much information about the relationship between the circuit performance y and the circuit parameters  $x_i$ , i = 1, 2, ..., n can be obtained from a full factorial experiment. The main or individual effect of a

|     | Parameter Levels |       | evels                 |                  | Interaction Levels |                  |                             |                       |

|-----|------------------|-------|-----------------------|------------------|--------------------|------------------|-----------------------------|-----------------------|

| Run | $x_1$            | $x_2$ | <i>x</i> <sub>3</sub> | $x_1 \times x_2$ | $x_1 \times x_3$   | $x_2 \times x_3$ | $x_1 \times x_2 \times x_3$ | y                     |

| 1   | -1               | -1    | -1                    | +1               | +1                 | +1               | -1                          | $y_1$                 |

| 2   | -1               | -1    | +1                    | +1               | -1                 | -1               | +1                          | $y_2$                 |

| 3   | -1               | +1    | -1                    | -1               | +1                 | -1               | +1                          | $y_3$                 |

| 4   | -1               | +1    | +1                    | -1               | -1                 | +1               | -1                          | $y_4$                 |

| 5   | +1               | -1    | -1                    | -1               | -1                 | +1               | +1                          | <i>y</i> <sub>5</sub> |

| 6   | +1               | -1    | +1                    | -1               | +1                 | -1               | -1                          | <i>y</i> <sub>6</sub> |

| 7   | +1               | +1    | -1                    | +1               | -1                 | -1               | -1                          | <i>y</i> <sub>7</sub> |

| 8   | +1               | +1    | +1                    | +1               | +1                 | +1               | +1                          | <i>y</i> <sub>8</sub> |

**TABLE 1.1** Full Factorial Design for n = 3

**FIGURE 1.2** Pictorial representation of full factorial design for n = 3.

parameter quantifies how much a parameter affects the performance singly. The main effect of  $x_i$ , denoted by  $v_i$ , is given by

$$v_i = \frac{1}{2^n} \sum_{k=1}^{2^n} x_{ik} \times y_k \tag{1.6}$$

where

$x_{ik}$  is the value of  $x_i$  in the kth run  $y_k$  is the corresponding performance value

Thus, the main effect is the difference between the average performance value when the parameter is at the high level (+1) and the average performance value when the parameter is at the

low level (-1). The main effect of  $x_i$  is the coefficient of the  $x_i$  term in the polynomial RSM of Equation 1.5. Similarly, the interaction effect of two or more parameters quantities how those factors jointly affect the performance. The two-factor interaction effect is computed as the difference between the average performance value when both factors are at the same level and the average performance value when they are at different levels. The two-factor interaction effect of parameters  $x_i$  and  $x_j$ , denoted by  $v_{i \times j}$ ,  $i \neq j$ , is defined as follows:

$$v_{i \times j} = \frac{1}{2} \left\{ v_{i|j=+1} - v_{i|j=-1} \right\}$$

$$= \frac{1}{2^n} \sum_{k=1}^{2^n} x_{ik} \times x_{jk} \times y_k$$

(1.7)

The two-factor interaction effect of  $x_i$  and  $x_j$ ,  $v_{i \times j}$ , is the coefficient of the  $x_i x_j$  terms in the quadratic RSM of Equation 1.5. Note that  $v_{i \times j}$  is the same as  $v_{j \times i}$ . Moreover, higher-order multifactor interaction effects can be computed recursively as before. Note that the interaction columns of Figure 1.2 are obtained by the aggregated "sign-multiplication" given in Equation 1.7.

Thus, the full factorial design allows us to estimate the coefficients of all the first-order and cross-factor second-order coefficients in the RMS of Equation 1.5. However, it does not allow us to estimate the coefficients of the pure quadratic term  $x_i^2$ . Moreover, the number of experimental runs increases exponentially with the number of circuit parameters; this may become impractical for a large number

|     | Para  | ameter Le | evels                 |                  |                             | Interaction I    | Levels                      |                       |

|-----|-------|-----------|-----------------------|------------------|-----------------------------|------------------|-----------------------------|-----------------------|

| Run | $x_1$ | $x_2$     | <i>x</i> <sub>3</sub> | $x_1 \times x_2$ | $\overline{x_1 \times x_3}$ | $x_2 \times x_3$ | $x_1 \times x_2 \times x_3$ | у                     |

| 1   | -1    | -1        | +1                    | +1               | -1                          | -1               | +1                          | $y_1$                 |

| 2   | -1    | +1        | -1                    | -1               | +1                          | -1               | +1                          | $y_2$                 |

| 3   | +1    | -1        | -1                    | -1               | -1                          | +1               | +1                          | <i>y</i> <sub>3</sub> |

| 4   | +1    | +1        | +1                    | +1               | +1                          | +1               | +1                          | $y_4$                 |

**TABLE 1.2** Half Fraction of a Full Factorial Design for n = 3

of circuit parameters. In many cases, high-order multifactor interactions are small and can be ignored. In such cases, it is possible to reduce the size of the design by systematically eliminating some interactions and considering only some of the runs. The accuracy with which the main effects and the low-order interaction effects are estimated does not have to be compromised. Such designs are called fractional factorial designs. The most popular class of fractional factorial designs are the  $2^{n-p}$  designs, where a  $1/2^p$ th fraction of the original  $2^n$  design is used. One of the half fractions of the  $2^3$  design shown in Table 1.1, i.e., a  $2^{3-1}$  design is shown in Table 1.2.

We observe that some of the columns of Table 1.2 are now identical. It can be seen from Equations 1.6 and 1.7 that we cannot distinguish between effects that correspond to identical columns. Such effects are said to be confounded or aliased with each other. From Table 1.2, we see that  $v_3$ , the main effect of  $x_3$ , and  $v_{1\times 2}$ , the interaction effects of  $x_1$  and  $x_2$ , are confounded with each other. Moreover the three-factor interaction effect  $v_{1\times 2\times 3}$  is confounded with the grand average of the performance (corresponding to a column of 1's). Confounding, however, is not really a problem, since in most applications, high-order interaction effects are negligible. For example, in the quadratic RSM of Equation 1.5, only main effects and two-factor interaction effects are important, and it can be assumed that all higher-order interaction effects are absent.

There is a systematic way of obtaining fractional factorial designs by first isolating a set of basic factors (circuit parameters) and then defining the remaining nonbasic factors in terms of the interaction of the basic factors. These interactions that define the nonbasic factors in terms of the basic factors are called generators. The set of basic factors and the generator functions completely characterize a fractional factorial design. For example, the generator function used in the example of Table 1.2 is

$$x_3 = x_1 \times x_2 \tag{1.8}$$

Note that, once the generator function is known for a fractional design, the confounding pattern is also completely known. Moreover, note that the generator functions are not unique. The generator functions  $x_1 = x_2 \times x_3$  and  $x_2 = x_1 \times x_3$  also give rise to the design of Table 1.2. This can be understood by realizing that a column corresponding to a parameter sign-multiplied by itself results in a column of all 1s, i.e., the identity column, denoted by I. Thus, multiplying both sides of Equation 1.8 by  $x_2$ , we get  $x_3 \times x_2 = x_1 \times x_2 \times x_2 = x_1 \times I = x_1$ , which is also a generator function. Thus, an appropriate set of generator functions must be defined.

Another important concept related to confounding is called the resolution of a design, which indicates the clarity with which individual effects and interaction effects can be evaluated in a design. A *resolution III* design is one in which no two main effects are confounded with each other (but they may be confounded with two-factor and/or higher-order interaction effects). An important class of resolution *III* designs is the saturated fractional factorial designs. Suppose that the number of factors (parameters), n, can be expressed as  $n = 2^q - 1$ , for some integer q. Then, a resolution *III* design can be obtained by first selecting q basic factors and then saturating the  $2^q$  design by assigning a nonbasic factor to each of the possible combinations of the q basic factors. There are p = n - q nonbasic factors and generator functions, and these

designs are called  $2_{\rm III}^{n-p}$  designs, since  $2^q=n+1$  runs are required for n factors. Note that the fractional factorial design of Table 1.2 is a  $2_{\rm III}^{n-p}$  design, with n=3 and p=1. In the saturated design for  $n=2^q-1$  factors, the confounding patterns for the basic and nonbasic factors are the same, which implies that any of the q factors may be chosen as the basic factors. However, if n+1 is not an integral power of 2, then q is chosen as  $q=[\log_2{(n+1)}]$ . Next, we define q basic factors and generate a  $2^q$  design. Next, we assign p=n-q nonbasic factors to p generators and form the  $2_{\rm III}^{n-p}$  design. Note that, in this case, only p of the  $2^q-q-1$  available generators are used, and the confounding pattern depends on the choice of the q basic factors and the p generators. The number of runs in the saturated design is considerably less than  $2\delta$ .

Another important class of designs commonly used is called *resolution V* designs. In these designs, no main effect or two-factor interaction effect is confounded with another main effect or two-factor interaction effect. Such designs are denoted by  $2_V^{n-p}$  designs, where as before, n is the number of factors and p is the number of generators. These designs can be used to estimate the coefficients of all but the pure quadratic terms in the RSM of Equation 1.5. Since the number of such coefficients (including the constant term) is C = 1 + n + n(n-1)/2, there must be at least C runs. Note that C is still substantially less than  $2^n$ . Another important advantage of the factorial designs is that they are orthogonal, which implies that the model coefficients can be estimated with minimum variances (or errors). An algorithmic method for deriving resolution V designs is given in [3].

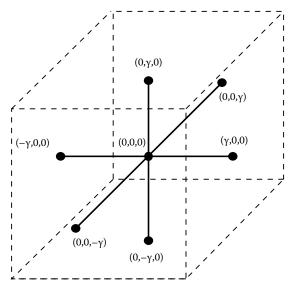

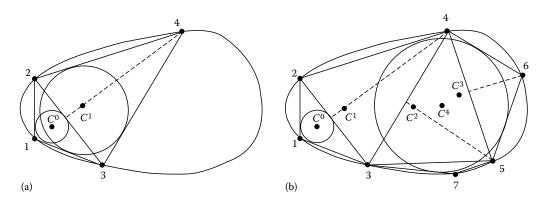

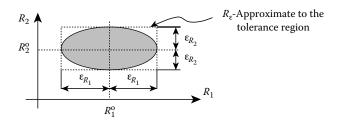

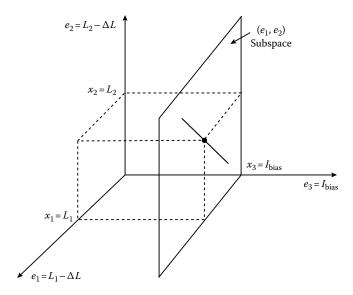

### 1.5.2 Central Composite Design

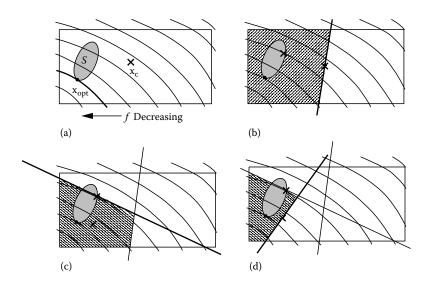

As mentioned previously, one of the problems of factorial designs in regard to the RMS of Equation 1.5 is that the coefficients of the pure quadratic terms cannot be estimated. These coefficients can be estimated by using a central composite design. A central composite design is a combination of a "cube" and a "star" subdesign. Each factor in a central composite design takes on five values:  $0, \pm 1$ , and  $\pm \gamma$ . Figure 1.3 shows the central composite design for the case of n=3. The cube subdesign, shown in dotted lines in Figure 1.3, is a fractional factorial design with the factor levels set to  $\pm 1$ . This design is of resolution V so that linear and cross-factor quadratic terms in the RSM of Equation 1.5 can be estimated. The star

**FIGURE 1.3** Central composite design for n = 3.

subdesign, shown in solid lines in Figure 1.3, is used to estimate the pure quadratic terms,  $x_1^2$ , in the RMS, and consists of

- One center point, where all the parameters are set to 0

- 2*n Axial* points, one pair for each parameter by setting its value to  $-\gamma$  and  $+\gamma$  and setting all other parameters to 0

The parameter  $\gamma$  (chosen by the user) is selected so that the composite plan satisfies the rotatability property [1]. The main advantage of the central composite design is that all the coefficients of Equation 1.5 can be estimated using a reasonable number of simulations.

### 1.5.3 Taguchi's Orthogonal Arrays

Taguchi's method using orthogonal arrays (OA) [4] is another popular experimental design technique. An orthogonal array is a special kind of fractional factorial design. These orthogonal arrays can be classified into two types. The first category of OAs corresponds to two-level designs, i.e., the parameters are quantized to two levels each, while the second corresponds to three-level designs, i.e., the parameters are quantized to three levels each. These arrays are often available as tables in books which discuss Taguchi techniques [4]. As an example, we show the L18 OA in Table 1.3. The number in the designation of the array refers to the number of experimental runs in the design. The L18 OA belongs to the second category of designs, i.e., each parameter has three levels. In the Taguchi technique, the experimental design matrix for the controllable or designable parameters is called the inner array, while that for the noise parameters is called the outer array. The L18 design of Table 1.3 can be used as an inner array as well as an outer array.

### 1.5.4 Latin Hypercube Sampling

The factorial, central composite, and Taguchi experimental designs described earlier set the parameters to certain levels or quantized values within their ranges. Therefore, most of the parameters space remains

| Run |   |   | P | aramet | er Leve | els |   |   |

|-----|---|---|---|--------|---------|-----|---|---|

| 1   | 1 | 1 | 1 | 1      | 1       | 1   | 1 | 1 |

| 2   | 1 | 1 | 2 | 2      | 2       | 2   | 2 | 2 |

| 3   | 1 | 1 | 3 | 3      | 3       | 3   | 3 | 3 |

| 4   | 1 | 2 | 1 | 1      | 2       | 2   | 3 | 3 |

| 5   | 1 | 2 | 2 | 2      | 3       | 3   | 1 | 1 |

| 6   | 1 | 2 | 3 | 3      | 1       | 1   | 2 | 2 |

| 7   | 1 | 3 | 1 | 1      | 1       | 3   | 2 | 3 |

| 8   | 1 | 3 | 2 | 3      | 2       | 1   | 3 | 1 |

| 9   | 1 | 3 | 3 | 1      | 3       | 2   | 1 | 2 |

| 10  | 2 | 1 | 1 | 3      | 3       | 2   | 2 | 1 |

| 11  | 2 | 1 | 2 | 1      | 1       | 3   | 3 | 2 |

| 12  | 2 | 1 | 3 | 2      | 2       | 1   | 1 | 3 |

| 13  | 2 | 2 | 1 | 2      | 3       | 1   | 3 | 2 |

| 14  | 2 | 2 | 2 | 3      | 1       | 2   | 1 | 3 |

| 15  | 2 | 2 | 3 | 1      | 2       | 3   | 2 | 1 |

| 16  | 2 | 3 | 1 | 3      | 2       | 3   | 1 | 2 |

| 17  | 2 | 3 | 2 | 1      | 3       | 1   | 2 | 3 |

| 18  | 2 | 3 | 3 | 2      | 1       | 2   | 3 | 1 |

TABLE 1.3 Taguchi's L18 OA

unsampled. It is therefore desirable to have a more "space-filling" sampling strategy. The most obvious method of obtaining a more complete coverage of the parameter space is to perform random or Monte Carlo sampling [5]. In random sampling, each parameter has a particular statistical distribution and the parameters are considered to be statistically independent. The distribution of the circuit parameters can often be obtained from test structure measurements followed by parameter extraction. Often, however, based on previous experience or reasonable expectation, the circuit parameters are considered to be normal (or Gaussian). Since the designable parameters are deterministic variables, they are considered to be independent and uniformly distributed for the purposes of random sampling. Random samples are easy to generate and many inferences can be drawn regarding the probability distribution of the performances. The problem with random sampling, however, is that a large sample is usually required to estimate quantities with sufficiently small errors. Moreover, circuit parameters are usually not statistically independent. In particular, the noise parameters are statistically correlated because of the sequential nature of semiconductor wafer processing. Further, a random sample may not be very space filling either. This can be understood by considering the bell-shaped Gaussian density curve. In random sampling, values near the peak of the bell-shaped curve would be more likely to occur in the sample since such values have higher probability of occurrence. In other words, values away from the central region would not be well represented in the sample.

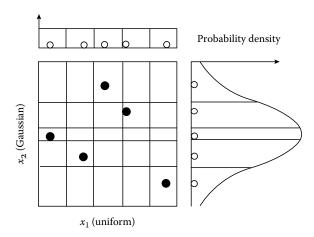

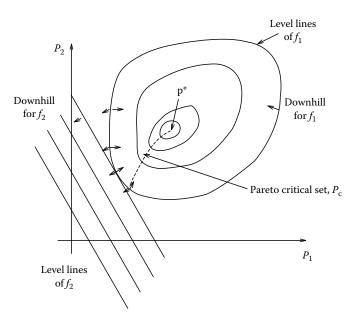

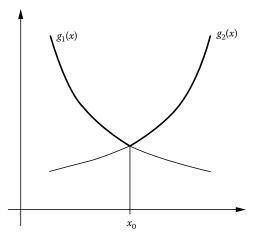

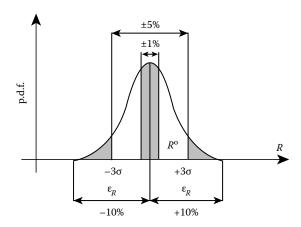

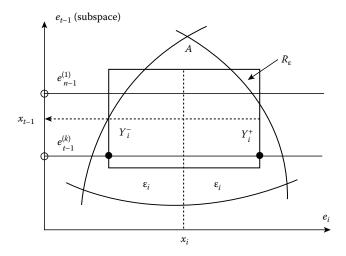

Latin hypercube sampling (LHS) [6,7] is a sampling strategy that alleviates this problem to a large extent. For each parameter  $x_i$ , all portions of its distribution are represented by sample values. If S is the desired size of the sample, then the range of each  $x_i$ , i=1, 2, ..., n is divided into S nonoverlapping intervals of equal marginal probability 1/S. Each such interval is sampled once with respect to the probability density in that interval to obtain S values for each parameter. Next, the S values for one parameter are randomly paired with the S values for another parameter, and so on. Figure 1.4 illustrates this process for the case of two circuit parameters  $x_1$  and  $x_2$ , where  $x_1$  is a uniform random variable, and  $x_2$  is a Gaussian random variable, and S=5. The marginal probability in an interval is defined as the area under the probability density curve for that interval. Therefore, intervals with equal probability are intervals with equal areas under the probability density curve. For the uniformly distributed  $x_1$ , equal probability intervals are also of equal length. For  $x_2$ , however, the intervals near the center are smaller (since the density there is higher) than the intervals away from the center (where the density is lower). Figure 1.4 shows that S=5 values are chosen from each region for  $x_1$  and  $x_2$  (shown as open circles). These values are then randomly paired so as to obtain the sample points (shown as filled dots). If the circuit parameters are correlated, then the pairing of the sample values can be controlled so that

FIGURE 1.4 Latin hypercube sampling for a uniform and a Gaussian random variable.

the sample correlation matrix is close to the user-provided correlation matrix for the circuit parameters. Note that LHS will provide a more uniform coverage of the parameter space than other experimental design techniques. Moreover, a sample of any size can be easily generated and all probability densities are handled.

### 1.6 Least-Squares Fitting

After the experimental design has been used to select the training points in the parameter space, the circuit is simulated at the training points and the values of the performance measure are extracted from the simulation results. Let S denote the number of experimental runs, and  $y_k$ , k = 1, ..., S denote the corresponding performance values. The aim in least-squares fitting is to determine the coefficients in the RSM so that the fitting error is minimized. Let C denote the number of coefficients in the RSM. For example, the value of C for the RSM of Equation 1.5 is C = (n+1)(n+2)/2, where n is the number of circuit parameters. There are interpolation-based methods that can be used to determine the coefficients when there are a smaller number of data points than coefficients, i.e., when S < C. One such method is called maximally flat quadratic interpolation and is discussed later in this chapter. We will restrict our discussion to the case of  $S \ge C$ . If S = C, then there are as many data points as coefficients, and simple simultaneous equation solving will provide the values of the coefficients. In this case, the model interpolates the data points exactly, and there is no fitting error to be minimized. When S > C, the coefficients can be determined in such a way that the fitting error is minimized. This method is called least-squares fitting (in a numerical analysis context) or linear regression (in a statistical context). The error measure is called the sum of squared errors and is given by

$$\in = \sum_{i=1}^{S} (y_k - \hat{y}_k)^2$$

(1.9)

where

$y_k$  denotes the simulated performance value

$\hat{y}_k$  denotes the model-predicted value at the kth data point

Least-squares fitting can then be stated as

$$\min_{\hat{\alpha}_i} \in \sum_{i=1}^{s} (y_k - \hat{y}_k)^2 \tag{1.10}$$

where  $\hat{\alpha}_i$  represents the (unknown) coefficients of the RSM. The error  $\varepsilon$  is used to determine the adequacy of the model. If this error is too large, the modeling procedure should be repeated with a larger number of training points or a different sampling strategy, or a different model of the performance may have to be hypothesized.

From a statistical point of view (linear regression), the actual performance value is considered to be

$$y_i = \hat{y}_i + e_i, \quad i = 1, 2, \dots, S$$

(1.11)

where  $e_i$  denotes the random error in the model. In least-squares fitting, this random error is implicitly assumed to be independent and identically distributed normal random variables with zero mean and constant variance. In particular, we assume that

$$E(e_i)=0$$

$$\mathrm{Var}(e_i)=\sigma^2$$

and  $\mathrm{Cov}(e_i,e_j)=0, \quad i\neq j$

If the RSM of the performance measure is linear, then it can be written as

$$\hat{y}(\mathbf{x}) = \sum_{i=1}^{C} \alpha_i f_i(\mathbf{x})$$

(1.13)

where

$f_i(\mathbf{x})$  are the known basis functions of the circuit parameters

C denotes the number of basis functions

Note that the RSM is said to be linear (and least-squares fitting can be used) if it is linear in terms of the model coefficients  $\alpha_i$ . The basis functions  $f_i(\mathbf{x})$  need not be linear. For instance, the basis functions used in the quadratic RSM of Equation 1.5 are 1,  $x_i$ , and  $x_ix_j$ .

Let **y** and **e** be S-vectors:  $\mathbf{y} = [y_1, \dots, y_S]^T$  and  $\mathbf{e} = [e_1, \dots, e_S]^T$ , where S is the number of data points. Also, let us define the model coefficients as  $\alpha = [\alpha_1, \dots, \alpha_C]$ . Finally, let **X** denote the following  $S \times C$  matrix:

$$X = \begin{bmatrix} f_1(\mathbf{x}_1) & \cdots & f_C(\mathbf{x}_1) \\ \vdots & \vdots & \vdots \\ f_1(\mathbf{x}_S) & \cdots & f_C(\mathbf{x}_S) \end{bmatrix}$$

(1.14)

Then, Equation 1.11 can be vectorially written as

$$\mathbf{y} = \mathbf{X}\alpha + \mathbf{e} \tag{1.15}$$

We choose  $\alpha$  to minimize the function

$$RSS(\alpha) = (\mathbf{y} - \mathbf{X}\alpha)^{\mathrm{T}}(\mathbf{y} - \mathbf{X}\alpha)$$

(1.16)

The least squares estimate  $\hat{\alpha}$  of  $\alpha$  is given by the following formula:

$$\hat{\alpha} = (\mathbf{X}^{\mathrm{T}}\mathbf{X})^{-1}\mathbf{X}^{\mathrm{T}}\mathbf{y} \tag{1.17}$$

The function Equation 1.16 evaluated at  $\hat{\alpha}$  is called the residual sum of squares, abbreviated RSS, and is given by

$$RSS = (\mathbf{v} - \mathbf{X}\hat{\alpha})^{\mathrm{T}}(\mathbf{v} - \mathbf{X}\hat{\alpha}) \tag{1.18}$$

It can be shown that an estimate of the variance of the random error is

$$\hat{\sigma}^2 = \frac{RSS}{S - C} \tag{1.19}$$

and that  $\hat{\alpha}$  is unbiased, i.e.,  $E(\hat{\alpha}) = \alpha$ , and the variance of the estimate is

$$\operatorname{var}(\hat{\alpha}) = \hat{\alpha}^2 (\mathbf{X}^{\mathrm{T}} \mathbf{X})^{-1} \tag{1.20}$$

Another figure of merit of the linear regression is called the coefficient of determination, denoted by  $R^2$ , and given by

$$R^{2} = 1 - \frac{\text{RSS}}{\sum_{i=1}^{s} (y_{1} - \bar{y})^{2}}$$

(1.21)

where  $\bar{y}$  is the sample average of the  $y_i$ s, i = 1, ..., S. The coefficient of determination measures the proportion of variability in the performance that is explained by the regression model. Values of  $R^2$  close to 1 are desirable.

### 1.7 Variable Screening

Variable screening is used in many performance modeling techniques as a preprocessing step to select the significant circuit parameters that are used as independent variables in the performance model. Variable screening can be used to substantially reduce the number of significant circuit parameters that must be considered, and thereby reduce the complexity of the analysis. The significant circuit parameters are included in the performance model, while the others are ignored. Several variable screening approaches have been proposed; in this chapter, we discuss a simple yet effective screening strategy that was proposed in [8].

The variable screening method of [8] is based on the two-level fractional factorial designs discussed earlier. We assume that the main effects (given by Equation 1.6) of the circuit parameters dominate over the interaction effects and this assumption enables us to use a resolution *III* design. Suppose that there are n original circuit parameters, denoted by  $x_1, \ldots, x_n$ . Then, we can use the simulation results from the fractional factorial design to compute the following quantities for each of the circuit parameters  $x_i$ ,  $i = 1, \ldots, n$ :

- 1. Main effect  $v_i$  computed using Equation 1.6

- 2. High deviation  $d_i^h$  from the nominal or center point, computed by

$$d_i^{\rm h} = \frac{2}{n_{\rm r}} \sum_{k \in K_i^+} y_k - y_{\rm c} \tag{1.22}$$

where

$n_{\rm r}$  is the number of simulations

$K_i^+$  is the set of indices where  $x_i$  is +1

$y_c$  is the performance value at the center point

3. The *low deviation*  $d_i^l$  from the center point, computed using a formula similar to Equation 1.22, with  $K_i^+$  replaced by  $K_i^-$

Note that only two of the preceding quantities are independent, since the third can be obtained as a linear combination of the other two. A statistical significance test is now used to determine if  $x_i$  is significant. To this end, we assume that the quantities  $v_i$ ,  $d_i^h$ , and  $d_i^l$  are sampled from a normal distribution with a sample size of n (since there are n circuit parameters). Denoting any one of the above quantities  $v_i$ ,  $d_i^h$ , or  $d_i^l$  by  $\delta_i$ , the hypothesis for the significance test is

Null hypothesis

$$H_0$$

:  $|\delta_i| = 0$ , i.e.,  $x_i$  is insignifiant

$$H_0 \text{ is rejected if } |\delta_i|/\sigma_\delta > t_{\alpha_s/2,n-1}$$

(1.23)

In Equation 1.23, a two-sided t-test is used [9] with significance level  $\alpha_s$  and  $\sigma_\delta$  denotes the estimate of the standard deviation of  $\delta_i \cdot t_{\alpha_s/2,n-1}$  denotes the value of the t statistic with significance level  $\alpha_s/2$  and degrees of freedom n-1. We declare a parameter  $x_i$  to be insignificant if it is accepted in the tests for at least two of  $v_i$ ,  $d_i^h$ , and  $d_i^l$ . This screening procedure is *optimistic* in the sense that an insignificant

parameter may be wrongly deemed significant from the preceding significance tests. The values of the *t*-variable can be read off from standard *t*-distribution tables available in many statistics text books.

### 1.8 Stochastic Performance Models

As stated earlier, the objective of performance modeling is to obtain an inexpensive surrogate to the circuit simulator. This performance model can then be used in a variety of deterministic and statistical optimization tasks in lieu of the expensive circuit simulator. The circuit simulator is a computer model, which is deterministic in the sense that replicate runs of the model with identical inputs will always result in the same values for the circuit performances. This lack of random error makes computer-based experiments fundamentally different from physical experiments. The experimental design and response surface modeling techniques presented earlier have the tacit assumption that the experiments are physical and the difference between the observed performance and the regression model behaves like white noise. In the absence of random error, the rationale for least-squares fitting of a response surface is not clear even though it can be looked upon solely as curve fitting. Stochastic performance modeling [10,11] has been used recently to model the outputs (in our case, the circuit performances) of computer codes or models (in our case, the circuit simulator). The basic idea is to consider the performances as realizations of a stochastic process and this allows one to compute a predictor of the response at untried inputs and allows estimation of the uncertainty of prediction.

The model for the deterministic performance y treats it as a realization of a stochastic process  $Y(\mathbf{x})$  which includes a regression model:

$$Y(\mathbf{x}) = \sum_{i=1}^{k} \alpha_i f_i(\mathbf{x}) + Z(\mathbf{x})$$

(1.24)

The first term in Equation 1.24 is the simple regression model for the performance and the second term represents the systematic departure of the actual performance from the regression model as a realization of a stochastic process. This model is used to choose a design that predicts the response well at untried inputs in the parameter space. Various criteria based on functionals of the means square error matrix are used to choose the optimal design. One the design is selected, the circuit simulator is exercised at those design points, and the circuit performance values are extracted. Next, a linear (in the model coefficients  $\hat{\alpha}_i s$ ) predictor is used to predict the values of the performance at untried points. This predicted value can be shown to be the sum of two components: the first component corresponds to the first term in Equation 1.24 and uses the generalized least squares estimate of the coefficients  $\alpha$ , and the second component is a smoothing term, obtained by interpolating the residuals at the experimental design points. The main drawback of the stochastic performance modeling approach is the excessive computational cost of obtaining the experimental design and of predicting the performance values.

### 1.9 Other Performance Modeling Approaches

The most popular performance modeling approach combines experimental design and least-squares-based response surface modeling techniques described previously [8,12–15]. A commonly used assumption valid for MOS circuits that has been used frequently is based on the existence of four critical noise parameters [16–18]. These four critical parameters are the flat-band voltage, the gate-oxide thickness, the channel length reduction, and the channel width reduction.

Several other performance modeling approaches have been proposed, especially in the context of statistical design of integrated circuits. One such approach is based on self-organizing methods [19] and is called the group method of data handling (GMDH) [20]. An interesting application of GMDH for performance modeling is presented in [21,22]. Another interesting approach is called maximally flat

quadratic interpolation (MFQI) [23]. A modeling approach combining the advantages of MFQI and GMDH is presented in [24]. It has been tacitly assumed in the discussion so far that a single RSM is sufficiently accurate to approximate the circuits performances over the entire circuit parameter space. This may not be true for many circuits. In such cases, a piecewise modeling approach may be used advantageously [8]. The circuit parameter space is divided into smaller regions, in each of which a single performance model is adequate. The continuous performance models in the various regions are then stitched together to preserve continuity across the regions.

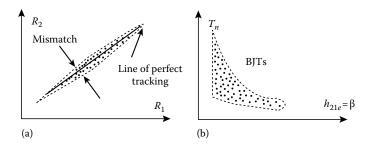

### 1.10 Example of Performance Modeling

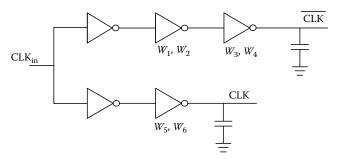

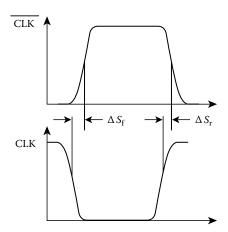

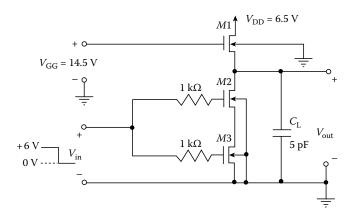

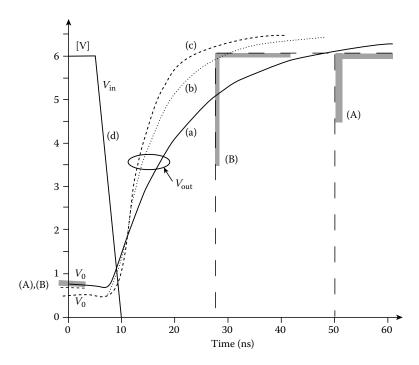

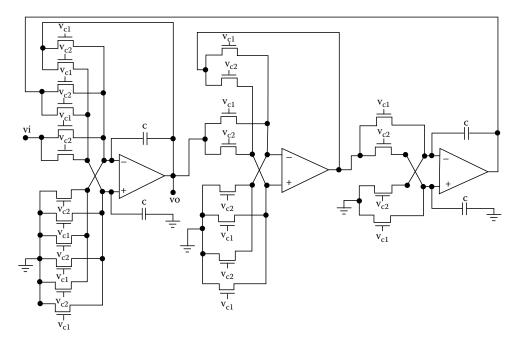

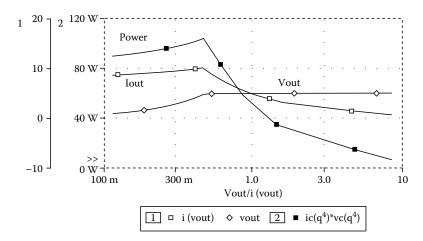

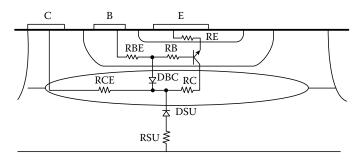

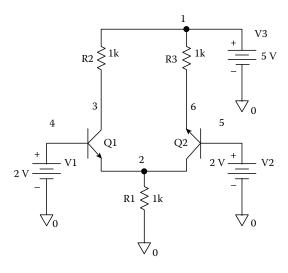

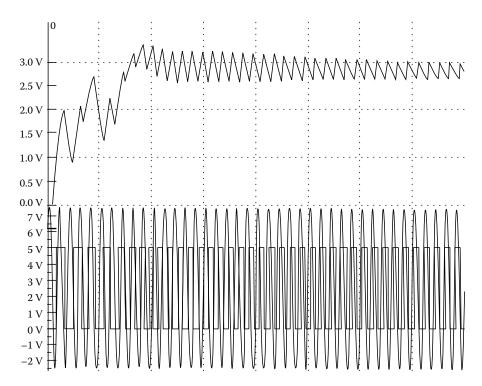

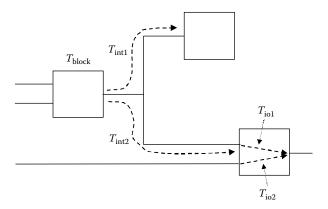

Below, we show an application of performance modeling applied to the clock skew of a clock distribution circuit. Consider the clock driver circuit shown in Figure 1.5. The top branch has three inverters and the lower branch has two inverters to illustrate the problem of signal skew present in many clock trees. We define the clock skew to be the difference between the times at which CLK and its complement cross a threshold of 0.5  $V_{\rm DD}$ . Two skews occur, as shown in Figure 1.6, one corresponding to the rising edge of the CLK,  $\Delta S_{\rm r}$ , and another corresponding to the falling edge of CLK,  $\Delta S_{\rm f}$ . The performance measure of interest is the signal skew  $\Delta S$  defined as the larger of the two skews.

The designable circuit parameters of interest in this example are the nominal channel widths of each of the transistors in the second and third inverters in the top branch and the last inverter in the lower

FIGURE 1.5 Clock distribution circuit.

FIGURE 1.6 Definition of rising and falling clock skews.

FIGURE 1.7 Plot of predicted versus simulated values for RSM of Equation 1.25.

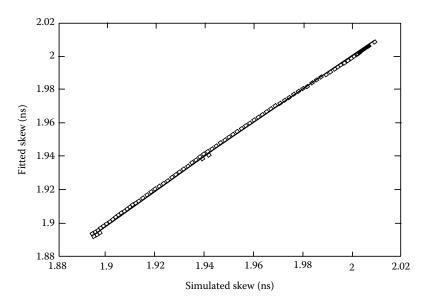

branch. The designable parameters are denoted by  $W_1$ ,  $W_2$ ,  $W_3$ ,  $W_4$ ,  $W_5$ , and  $W_6$  and are marked in Figure 1.5. The noise parameters of interest are the random variations in the channel widths and lengths of all nMOS and pMOS transistors in the circuit, and the common gate oxide thickness of all the transistors. These are denoted by  $\Delta W_n$  (channel width variation of nMOS transistors),  $\Delta L_n$  (channel length variation nMOS transistors),  $\Delta W_p$  (channel width variation of pMOS transistors),  $\Delta L_p$  (channel length variation of pMOS transistors), and  $t_{ox}$  (gate oxide thickness of all nMOS and pMOS transistors). We hypothesize a linear RSM for the clock skew in terms of the designable and noise parameters of the circuit. To this end, we generate an experimental design of size 30 using Latin hypercube sampling. The circuit is simulated at each of these 30 training points, and the value of the clock skew  $\Delta S$  is extracted from the simulation results. Then, we use regression to fit the following linear RSM:

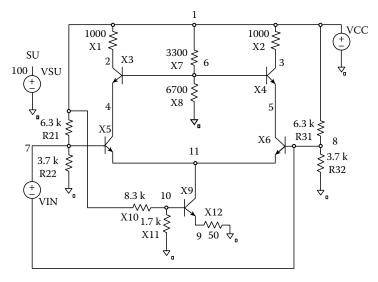

$$\Delta S = 1.93975 - 0.0106W_1 + 0.0121W_2 + 0.0045W_3 - 0.1793W_4 + 0.0400W_5 + 0.0129W_6 - 0.0149\Delta W_n - 0.0380\Delta W_p - 0.0091\Delta L_n + 0.0115\Delta L_p + 0.161t_{ox}$$

(1.25)

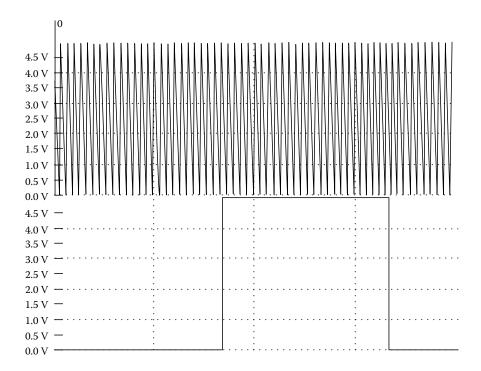

This RSM has an  $R^2$  of 0.999. The prediction accuracy for the preceding RSM is in Figure 1.7 where the values of  $\Delta S$  predicted from the RSM are plotted against the simulated values for a set of checking points (different from the training points used to fit the RSM). Most of the points lie near the 45° line indicating that the predicted values are in close agreement with the simulated values.

### References

- G. E. P. Box and N. R. Draper, Empirical Model Building and Response Surfaces, New York: Wiley, 1987.

- 2. G. E. P. Box, W. G. Hunter, and J. S. Hunter, *Statistics for Experimenters: An Introduction to Design, Data Analysis, and Model Building*, New York: Wiley, 1987.

- 3. N. R. Draper and T. J. Mitchell, The construction of saturated  $2_R^{k-p}$  designs, *Ann. Math. Stat.*, 38: 1110–1126, August 1967.

- 4. P. J. Ross, Taguchi Techniques for Quality Engineering, New York: McGraw-Hill, 1988.

- 5. J. M. Hammersley and D. C. Handscomb, *Monte Carlo Methods*, London: Methuen and Co. Ltd., 1964.

- M. D. McKay, R. J. Beckman, and W. J. Conover, A comparison of three methods for selecting values

of input variables in the analysis of output from a computer code, *Technometrics*, 21: 239–245,

May 1979.

- 7. R. L. Iman and W. J. Conover, A distribution-free approach to inducing rank correlations among input variables, *Commn. Stat.*, B11(3): 311–334, 1982.

- 8. K. K. Low and S. W. Director, An efficient methodology for building macromodels of IC fabrication processes, *IEEE Trans. Comput. Aided Des.*, 8: 1299–1313, December 1989.

- 9. D. C. Montgomery and E. A. Peck, *Introduction to Linear Regression Analysis*, New York: Wiley, 1982.

- 10. J. Sacks, W. J. Welch, T. J. Mitchell, and H. P. Wynn, Design and analysis of computer experiments, *Stat. Sci.*, 4(4): 409–435, 1989.

- 11. M. C. Bernardo, R. Buck, L. Liu, W. A. Nazaret, J. Sacks, and W. J. Welch, Integrated circuit design optimization using a sequential strategy, *IEEE Trans. Comput. Aided Des.*, 11: 361–372, March 1992.

- 12. T. K. Yu, S. M. Kang, I. N. Hajj, and T. N. Trick, Statistical modeling of VLSI circuit performances, *Proceedings of the IEEE International Conference Computer-Aided Design*, Santa Clara, CA, November 1986, pp. 224–227.

- T. K. Yu, S. M. Kang, I. N. Hajj, and T. N. Trick, Statistical performance modeling and parametric yield estimation of MOS VLSI, *IEEE Trans. Comput. Aided Des.*, CAD-6: 1013–1022, November 1987.

- 14. T. K. Yu, S. M. Kang, W. Welch, and J. Sacks, Parametric yield optimization of CMOS analog circuits by quadratic statistical performance models, *Int. J. Circuit Theory Appl.*, 19: 579–592, November 1991.

- 15. A. Dharchoudhury and S. M. Kang, An integrated approach to realistic worst-case design optimization of MOS analog circuits, *Proceedings of the 29th ACM/IEEE Design Automation Conference*, Anaheim, CA, June 1992, pp. 704–709.

- 16. P. Cox, P. Yang, S. S. Mahant-Shetti, and P. Chatterjee, Statistical modeling for efficient parametric yield estimation, *IEEE J. Solid State Circuits*, SC-20: 391–398, February 1985.

- 17. P. Yang and P. Chatterjee, Statistical modeling of small geometry MOSFETs, *IEEE International Electron Device Meeting*, San Franscisco, CA, December 1982, pp. 286–289.

- 18. P. Yang, D. E. Hocevar, P. Cox., C. Machala, and P. Chatterjee, An integrated and efficient approach for MOS VLSI statistical circuit design, *IEEE Trans. Comput. Aided Des.*, 5: 5–14, January 1986.

- 19. S. J. Farlow, Ed., Self-Organizing Methods in Modeling: GMDH Type Algorithms, New York: Marcel Dekker, 1984.

- 20. A. G. Ivakhnenko, The group method of data handling, a rival of the method of stochastic approximation, *Sov. Autom. Control*, 13(3): 43–45, 1968.

- 21. A. J. Strojwas and S. W. Director, An efficient algorithm for parametric fault simulation of monolithic IC's, *IEEE Trans. Comput. Aided Des.*, 10: 1049–1058, August 1991.

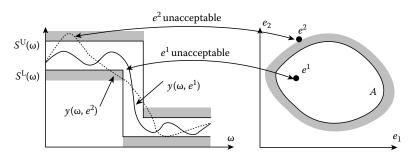

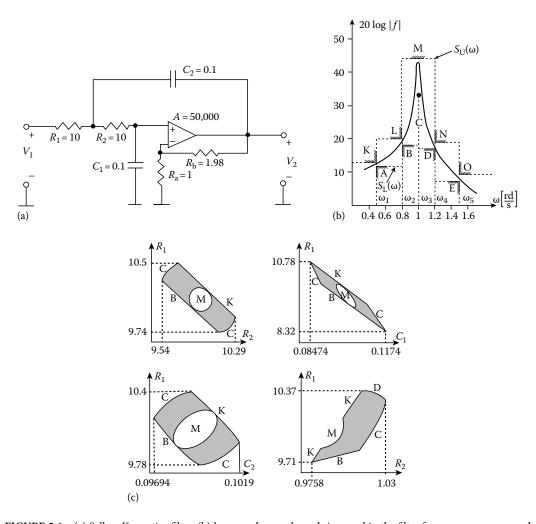

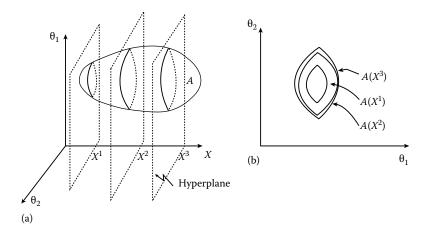

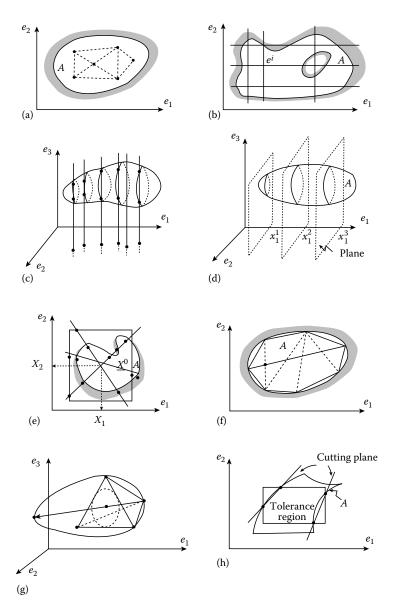

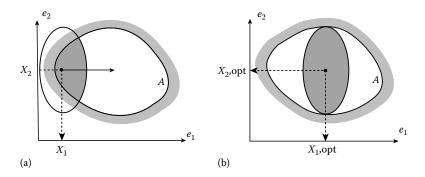

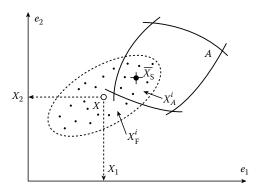

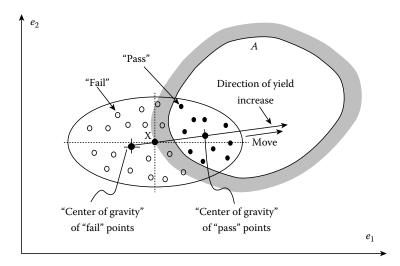

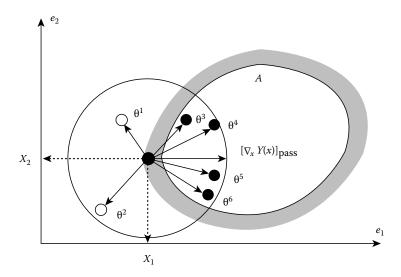

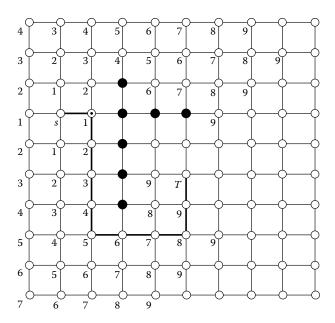

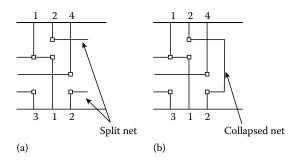

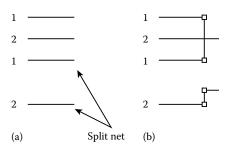

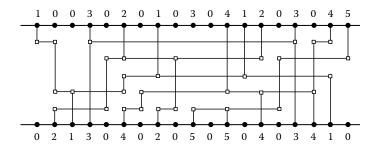

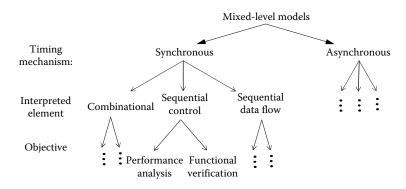

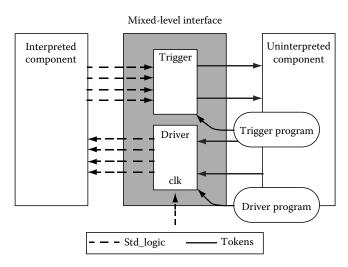

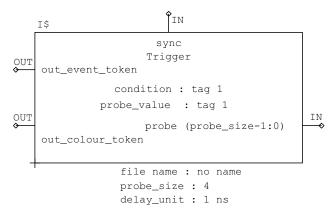

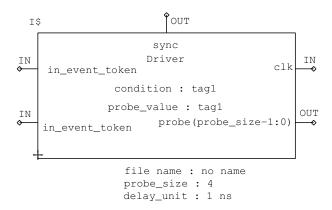

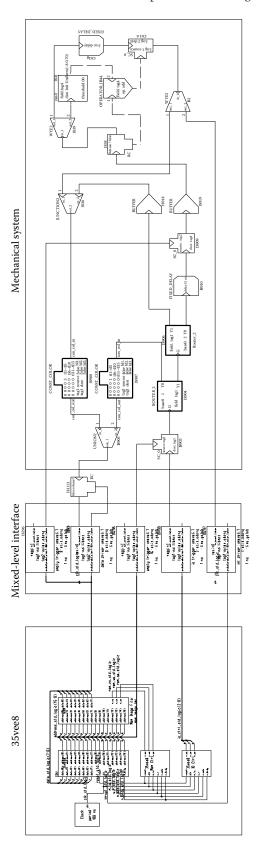

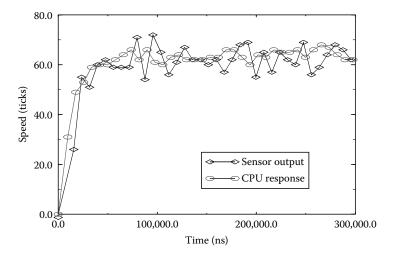

- 22. S. Ikeda, M. Ochiai, and Y. Sawaragi, Sequential GMDH and its application to river flow prediction, *IEEE Trans. Syst. Man Cybern.*, SMC-6: 473–479, July 1976.